标签:需要 code pcb 时钟 开发者 thinking 技术 关系 ima

前言

两年时间使用了三款ADC:AD9653,AD9266,AD3442,在此记录下坑及使用经验。

参考文档

xapp524-serial-lvds-adc-interface.pdf

所需用到的原语:IDDR、ISERDESE2等

1.AD9653:ADI公司的采样率高达125M,16bit ADC

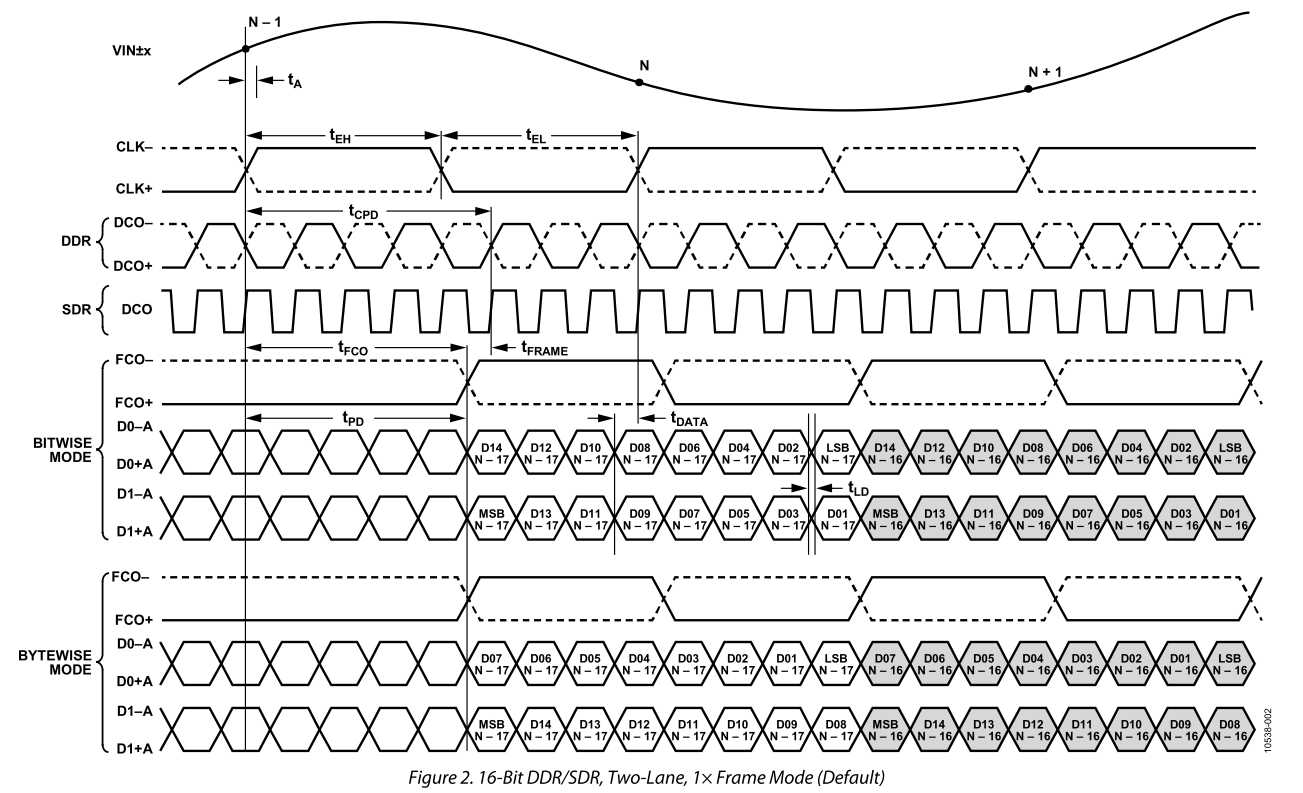

时序图1:

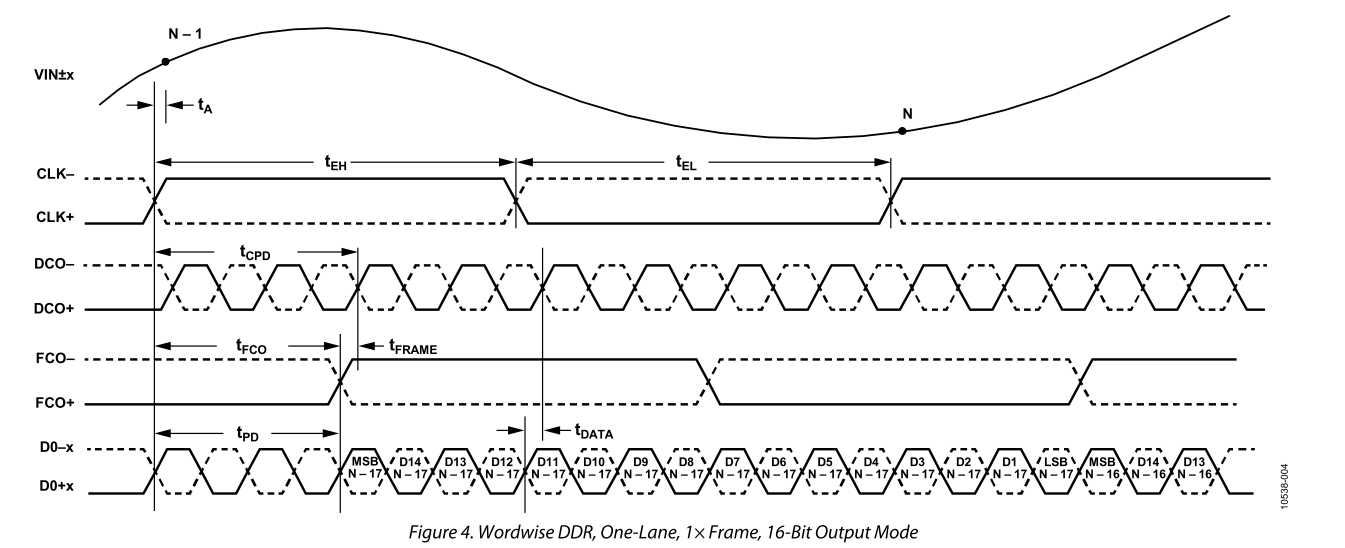

时序图2:

根据时序图,可使用ISERDESE2进行解串。

对于xilinx7系列的FPGA,DDR模式的ISERDESE2支持4、6、8bit,级联支持10、14bit。对于SDR模式的ISERDESE2支持2,3,4,5,6,7,8bit。

则对于16bit的ADC,可使用SDR或DDR模式,且ADC需配置为双线,即为时序图1的时序。

2.AD9266:16bit ADI公司的高达80M采样的ADC

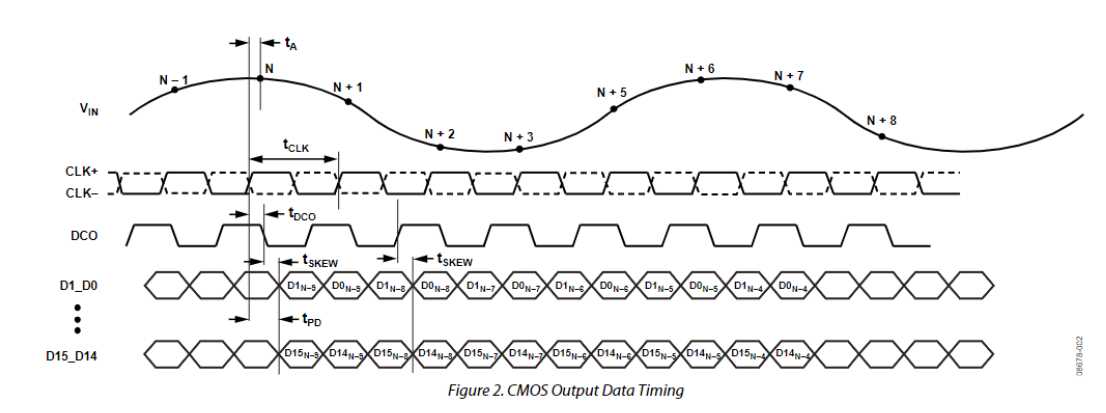

时序图1:

可以看到数据是并行的8个通道,DDR。则可以使用IDDR进行接收。

3.AD3442:TI公司14bit高达50M采样的ADC。

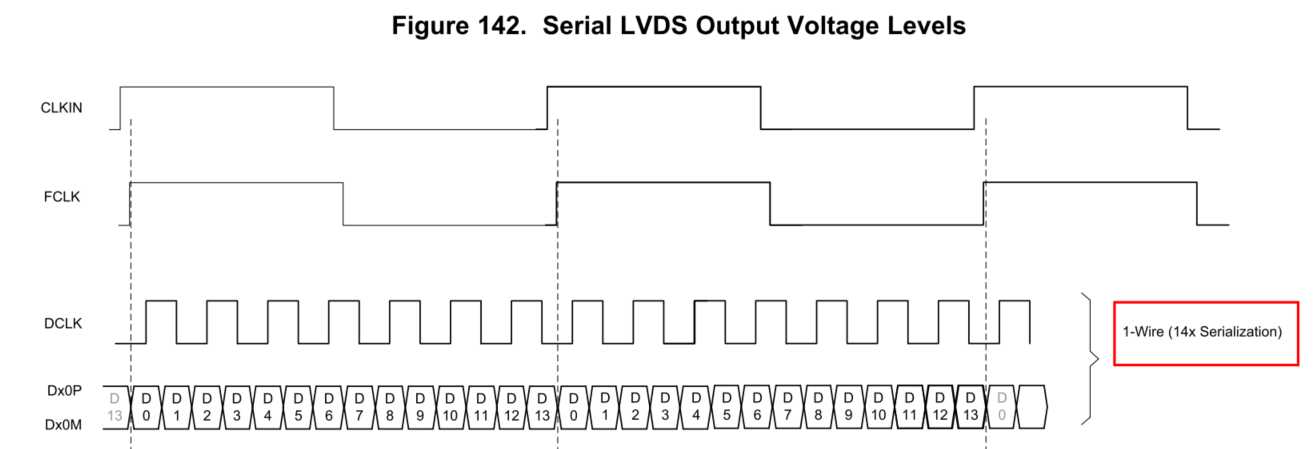

时序图1:

时序图2:

这里简单起见,使用时序图1 进行ISERDESE2解串处理,14bit的数据可用级联DDR模式。

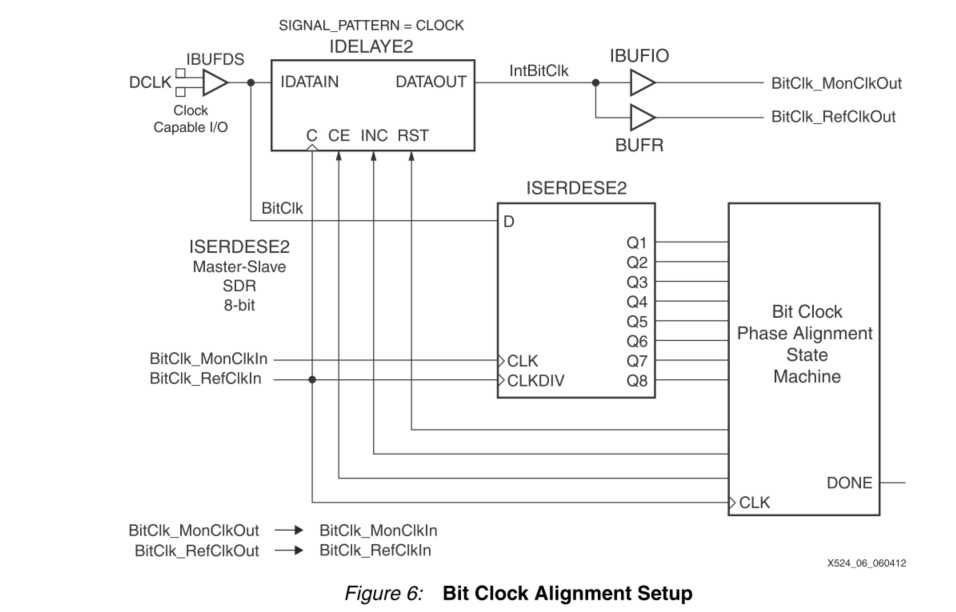

参考文档中的图,下述图主要用于调整经过IBUFIO或BUFR的时钟边沿跟经过IBUFDS的时钟边沿对齐。使得LVDS数据和时钟均只经过IBUFDS,保证相位关系。

然后用ISERDESE2接收数据,根据实际情况是否使用IDELAY模块对数据进行延时,使得数据尽量对齐中心边沿,当然如果PCB保证了数据和时钟的等长处理则更佳,只需考虑高低温情况的偏斜。

需考虑bit调整,其次需要字节对齐,因为解串出来的数据第一个bit是随机的,不一定就是所需的数据,需要进行字节训练,保证解串出的值的正确性。

上述两个步骤操作完成后,就可以放心采集数据了。

Thinking:高速率情况应该也可使用双线级联DDR14bit模式,对数据进行拆分。

使用IDDR和ISERDESE2主要关注时钟与数据的关系,要开发者保证时序关系确保接收数据的准确性。

以上。

标签:需要 code pcb 时钟 开发者 thinking 技术 关系 ima

原文地址:https://www.cnblogs.com/kingstacker/p/13266679.html