标签:begin 图片 没有 alt initial mic 使用 仿真 verilog

在数字电路中,时钟信号是重要的一类信号,一般作为激励源驱动时序电路。掌握时钟信号的编写,对于时序电路的仿真具有重要意义。所有的时序电路都需要设置时钟信号来确认时序。这里先写一个已知时间间隔的简易时钟信号。

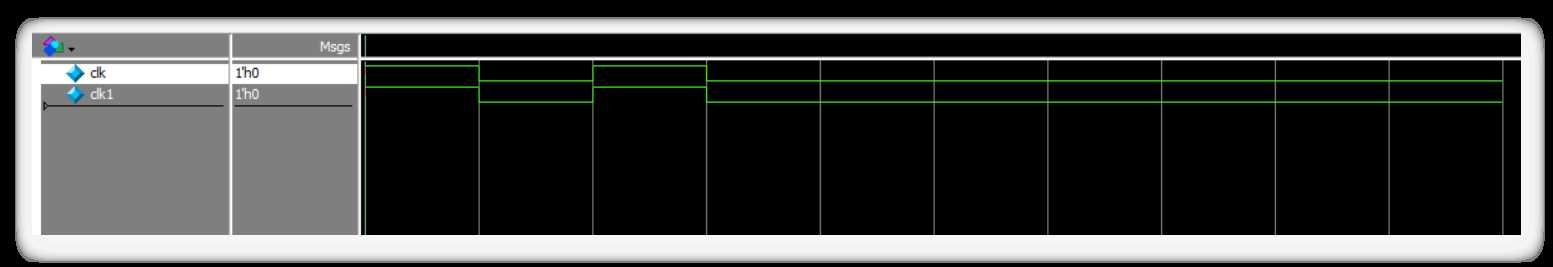

initial begin clk=1; #1 clk=0; #1 clk=1; #1 clk=0; end

这个编写的逻辑非常简单,就是根据时钟信号的特点,一个时钟周期变一次,根据所需的时间长度确认重复的次数。

initial fork clk1=1; #1 clk1=0; #2 clk1=1; #3 clk1=0; #10 $stop(); join

这个代码是使用同步进行的fork-join来实现的。这里可以看出延时时间是绝对的,不包含前面的延时。这里也可以看出每个语句之间是没有优先级的。

可以看到来个信号的结果是一致的。使用initial语句实现信号可以直接表示每个时间段的信号变化。对于其他测试向量来说,也可以使用这种精确的方法实现信号源的编写。但是,在比较大的设计中,时钟信号一般需要作用比较长的时间,使用initial会占用大量的空间。对于高度重复的信号源,可以使用always块来实现。always块可以一直循环执行,知道仿真结束。

标签:begin 图片 没有 alt initial mic 使用 仿真 verilog

原文地址:https://www.cnblogs.com/electricdream/p/13307717.html