标签:占空比 无法 模拟 alt 激励 image 一个 style span

时钟信号除了可以根据时序一个个变化列举出来,还可以利用其循环的变化的特点,使用循环执行语句always来实现。这种方法实现的时钟信号可以一直执行且不需要关注每个变化点的延时。

initial begin clk=0; clk1=0; clk2=0; end //way1 always #1 clk=~clk; //way2 always begin #1 clk1=~clk1; #1 clk2=~clk2; end

方法1是最方便的时钟信号,只有一条执行语句,甚至不需要使用块来封装。

方法2则是使用begin-end来实现两个时钟信号clk1和clk2,可以简单地分析出clk2的周期是clk1的两倍。clk1是2系统周期,clk2是4系统周期。占空比就是50%,一条语句是无法实现其他占空比的时钟信号的。

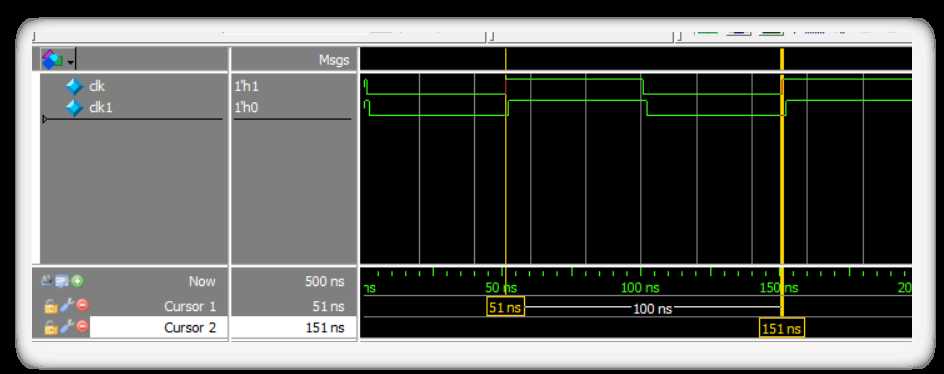

initial begin clk=1; clk1=1; end always fork #1 clk=~clk; #2 clk1=~clk1; #3 ; #50 ; join

可以观察到fork-join的时钟信号的周期是最大延时的两倍。每个时钟信号的周期都是一致的。其他延时只会改变时钟信号的相位。从这里也可以看出fork-join的块的工作原理:先找到最大延时,其他延时执行语句在其子期间中显示。使用fork-join可以仿真有时钟延时的信号输入。

使用循环执行语句来实现时钟信号是常用的方法。一般的时钟信号的激励也是利用循环执行来模拟的。

标签:占空比 无法 模拟 alt 激励 image 一个 style span

原文地址:https://www.cnblogs.com/electricdream/p/13326438.html