标签:efi 运算 ima *** bsp 相加 mic def alt

先暂存

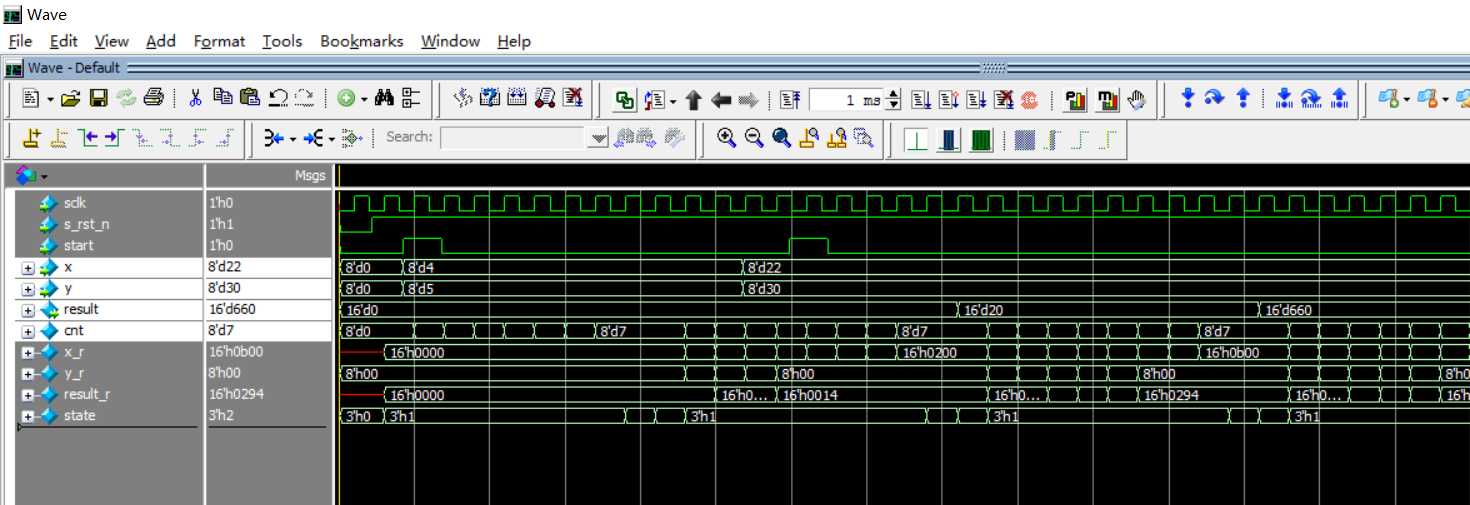

1 module mul_add( 2 input sclk , 3 input s_rst_n , 4 5 //input start , 6 input [7:0] x , // 乘数 7 input [7:0] y , // 被乘数 8 9 output reg [15:0] result 10 ); 11 12 //========================================================================13 // =========== Define Parameter and Internal signals =========== 14 //========================================================================/ 15 reg [7:0] cnt ; 16 reg [15:0] x_r ; // 乘数的中间变量 17 reg [7:0] y_r ; // 被乘数的中间变量 18 reg [15:0] result_r ; // 运算结果的中间变量 19 reg [2:0] state ; // 20 21 parameter S0 = 3‘d0 ; 22 parameter S1 = 3‘d1 ; 23 parameter S2 = 3‘d2 ; 24 25 //============================================================================= 26 //**************************** Main Code ******************************* 27 //============================================================================= 28 29 30 31 always @ (posedge sclk or negedge s_rst_n) begin 32 if(s_rst_n == 1‘b0) begin 33 result <= 0; 34 cnt <= 0; 35 y_r <= 0; 36 state <= S0; 37 end 38 else begin 39 case(state) 40 S0:begin 41 x_r <= {8‘d0,x}; 42 y_r <= y; 43 cnt <= 0; 44 result_r <= 0; 45 state <= S1; 46 end 47 48 S1:begin 49 if(cnt == 7) 50 state <= S2; 51 else begin 52 if(y_r[0] == 1‘b1) 53 result_r <= result_r + x_r; // 和左移零位相似 54 else 55 result_r <= result_r; 56 y_r <= y_r >> 1; // 被乘数右移一位 57 x_r <= x_r << 1; // 乘加一次后,被乘数左移一位 58 cnt <= cnt + 1‘b1; 59 state <= S1; 60 end 61 end 62 63 S2:begin 64 result <= result_r; 65 state <= S0; 66 end 67 default:; 68 endcase 69 end 70 end 71 endmodule

标签:efi 运算 ima *** bsp 相加 mic def alt

原文地址:https://www.cnblogs.com/571328401-/p/13341391.html