标签:时间 sign 解析 lse 地方 完成 pre color end

fifo,就是缓存器,可以理解为升级版的D触发器。D触发器是在时钟信号的控制下,数据等时间间隔刷新。对于fifo而言,数据也是需要刷新的,不过有一个读取控制信号决定数据是否读取。还有一个区别就是输入是与储存数据脱钩的。有写入控制信号决定是否连接。还有一些数据是否溢出、数据是否为初始状态等指示性信号,这里就不多说明了,作用和电路中的指示灯差不多。先做一个简单的fifo模型看一下实际的原理吧。

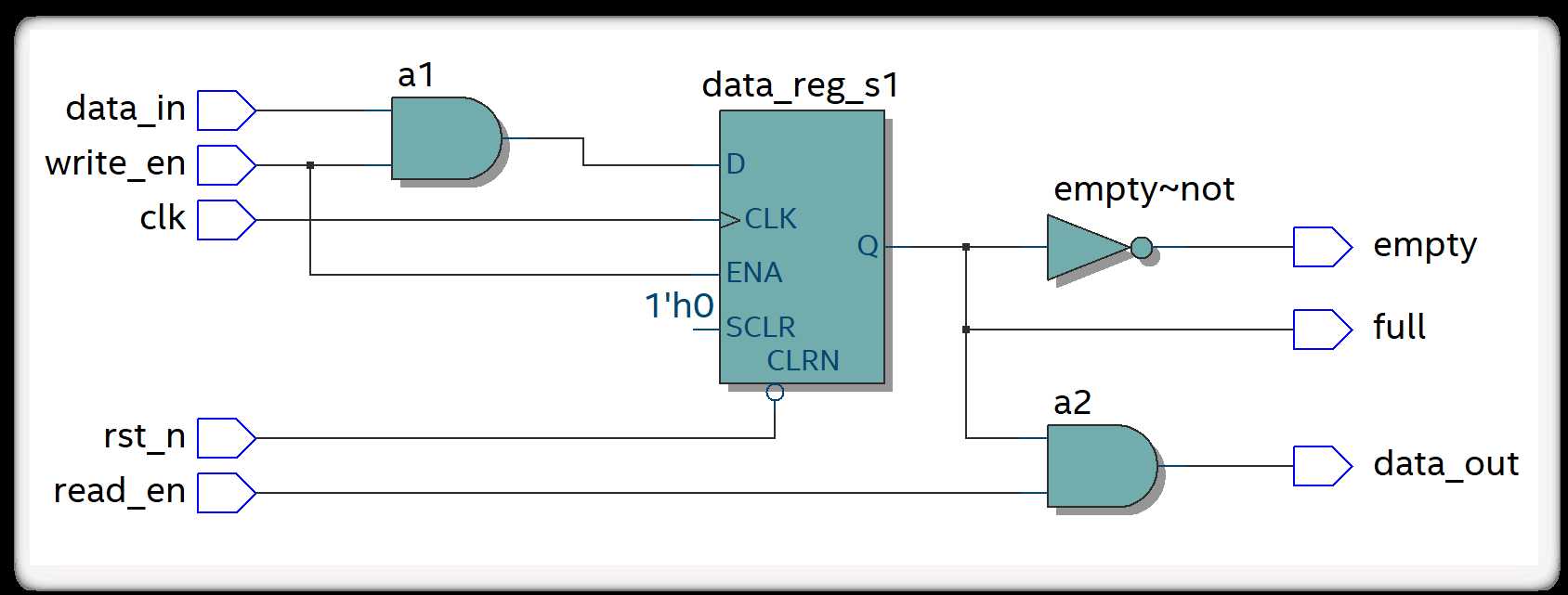

module demo_little_fifo( input wire clk, input wire rst_n, input wire data_in, input wire write_en, input wire read_en, output wire data_out, output wire full, output wire empty ); wire data_write; reg data_reg_s1; wire data_read; and a1(data_write,data_in,write_en); always@(posedge clk or negedge rst_n)begin if(!rst_n)begin data_reg_s1<=1‘b0; end else if(write_en) begin data_reg_s1<=data_write; end end and a2(data_read,data_reg_s1,read_en); assign data_out=data_read; assign full=(data_reg_s1==1‘b1)? 1‘b1:1‘b0; assign empty=(data_reg_s1==1‘b0)? 1‘b1:1‘b0; endmodule

RTL视角分析

这里是一个简易fifo,写入速率由时钟控制,读取速率为直接读取。具有数据写入和读取的控制位,也具有指示数据状态的简易指示(这里其实就是对值的高低判断,不是是否有值的判断)。当然,对于一个复杂的fifo,还会有许多其他的模块。这里只是用于说明原理。

具体的fifo的功能实现,有时间再去完成。现在大致了解原理后就可以用于使用了。使用fifo的地方还是比较多的。在数据的缓存截取和跨时钟中,fifo都是必不可少的。

标签:时间 sign 解析 lse 地方 完成 pre color end

原文地址:https://www.cnblogs.com/electricdream/p/13224926.html