标签:ops get setup 兼容 bsp 文本 模块 路径 pre

设置、库和对象

setup 、library、object

Sysnopsys提供了一个例子,在下面的位置:

$synopsys/doc/syn/guidelines

首先,可以在.synopsys_dc.setup里面设置库的位置和一些环境变量。里面包括所使用库的位置,DC涉及到几个库文件:

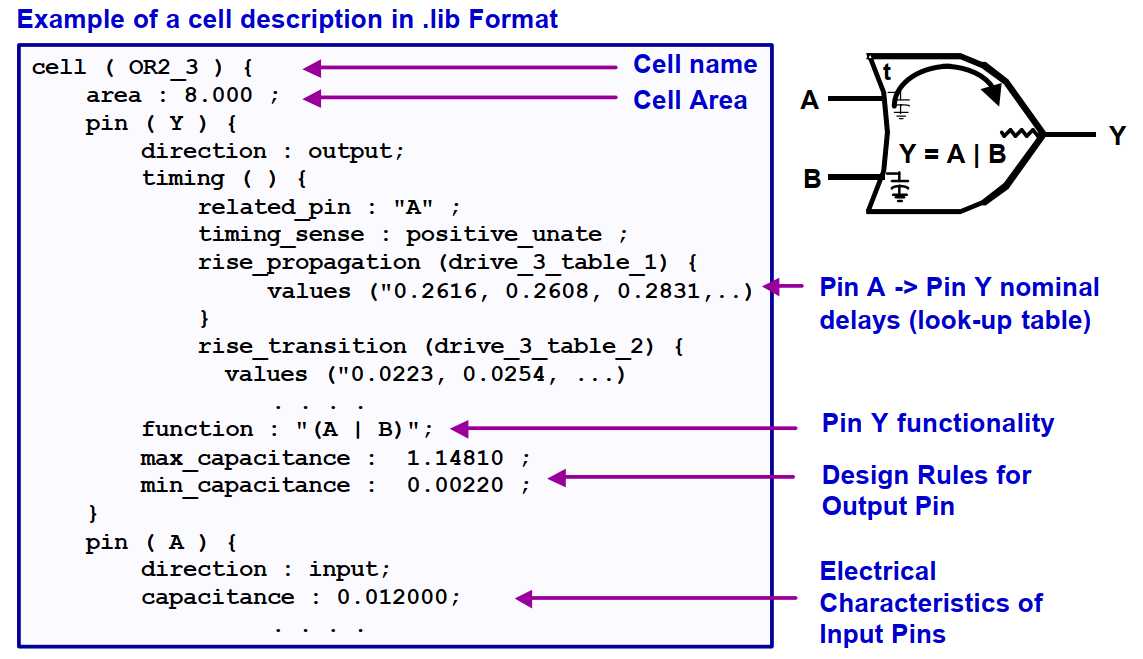

1、 工艺库(target_library):工艺库是综合后电路网表要最终映射到的库,读入的HDL代码首先由synopsys自带的GTECH库转换成Design Compiler内部交换的格式,然后经过映射到工艺库和优化生成门级网表。工艺库是由Foundary提供的,一般是.db的格式。这种格式是DC认识的一种内部文件格式,不能由文本方式打开。.db格式可以由文本格式的.lib转化过来,他们包含的信息是一致的。

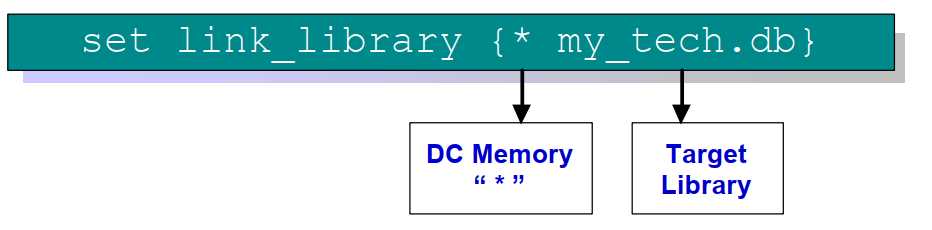

2、 链接库(link_library):link_library设置模块或者单元电路的引用,对于所有DC可能用到的库,我们都需要在link_library中指定,其中也包括要用到的IP。此处还要将search_path加进来,这样才能找到.db文件,否则只会搜索当前目录。

3、 符号库 (symbol_library):symbol_library是定义了单元电路显示的Schematic的库。用户如果想启动design_analyzer或design_vision来查看、分析电路时需要设置symbol_library。符号库的后缀是.sdb,加入没有设置,DC会用默认的符号库取代。

4、 综合库(synthetic_library):在初始化DC的时候,不需要设置标准的DesignWare库standard.sldb用于实现Verilog描述的运算符,对于扩展的DesignWare,需要在synthetic_library中设置,同时需要在link_library中设置相应的库以使得在链接的时候DC可以搜索到相应运算符的实现。

当DC映射电路时,它如何知道你在使用哪个单元库?

它如何知道 cells 的时间?您的ASIC供应商必须提供一个dc兼容的技术库!

例如以下供应商提供的异或门电路的电路库

目标库是设计编译器用来构建电路的库。

在映射过程中,DC将:

1)从这个库中选择功能正确的门

2)使用供应商提供的这些门的timing数据计算电路的时间。

目标库是DC中的保留变量

将其设置为指向silicon硅供应商提供的库文件

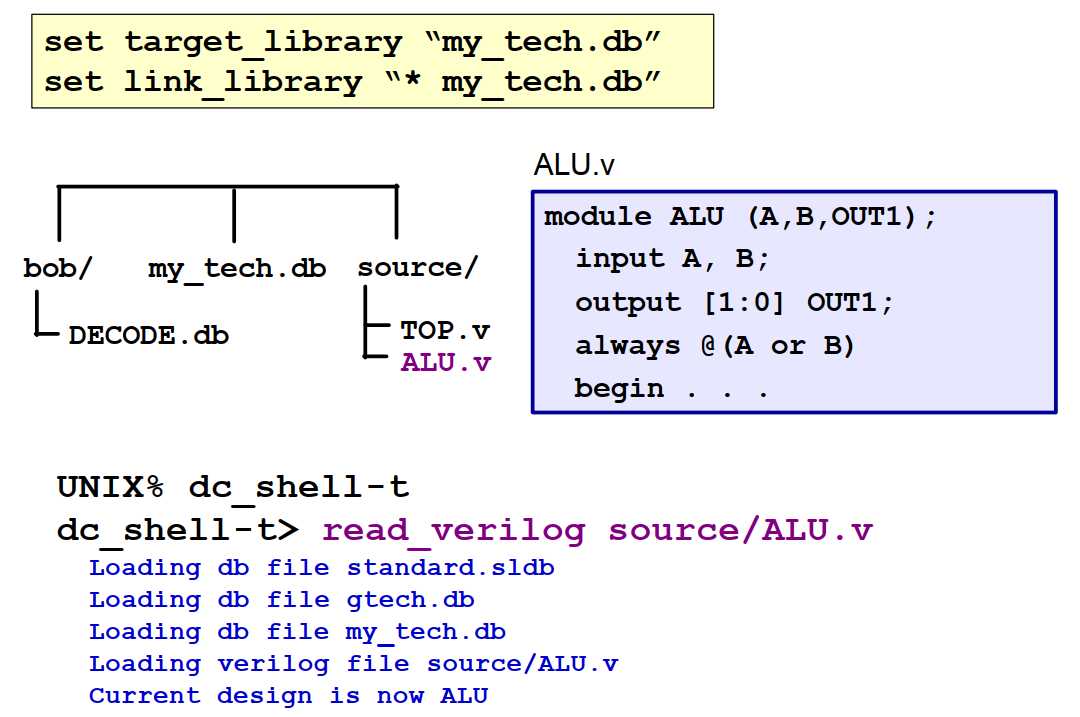

set target_library my_tech.db

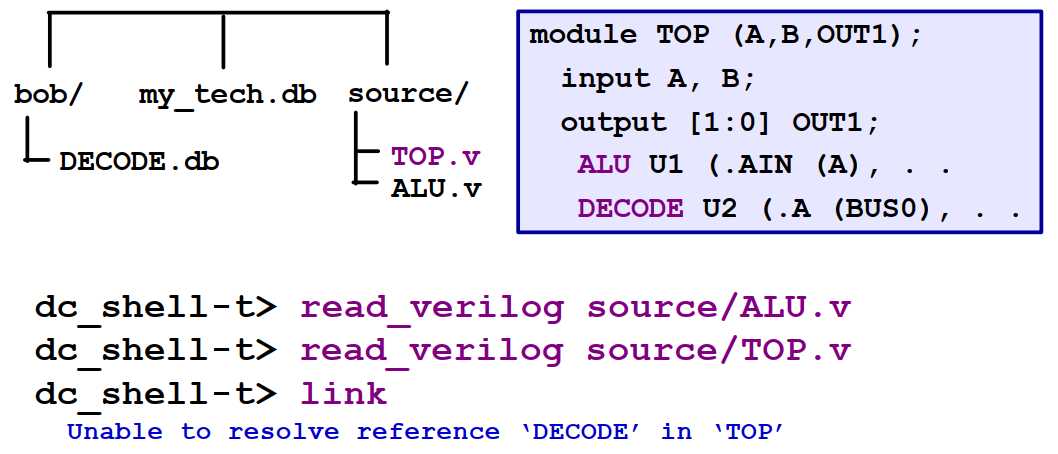

用于解析设计参考设置链接库:

首先搜索memory ,然后搜索链接库变量 link_library variable中指定的库文件。

第二,DC搜索在搜索路径变量search_path中定义的所有路径

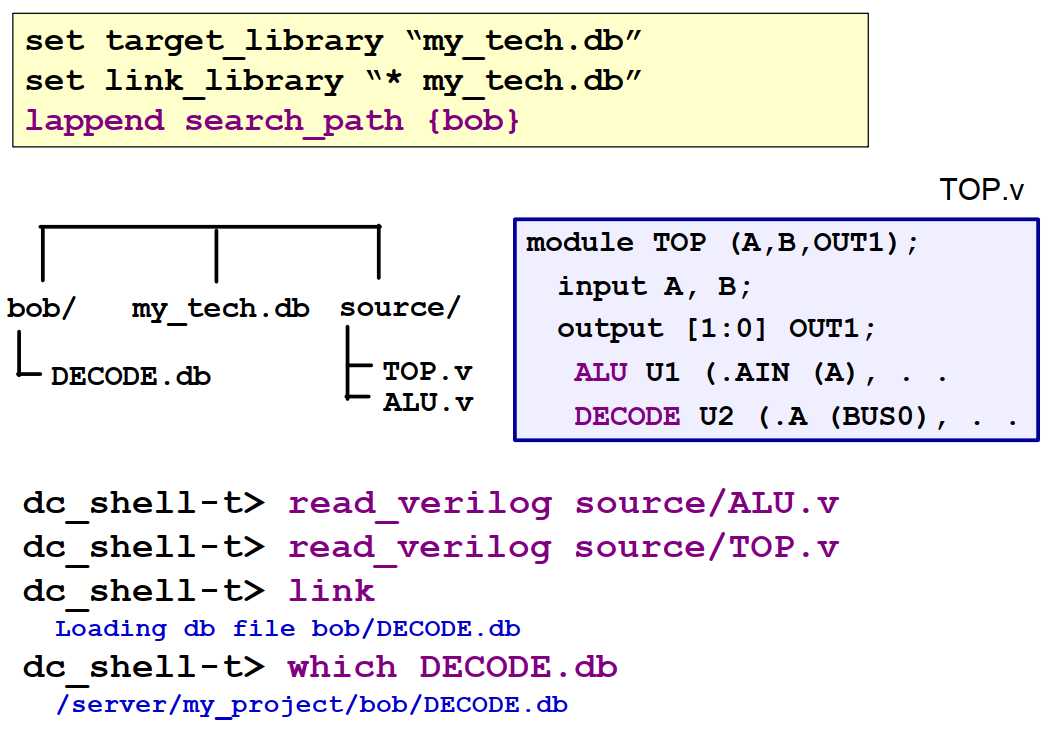

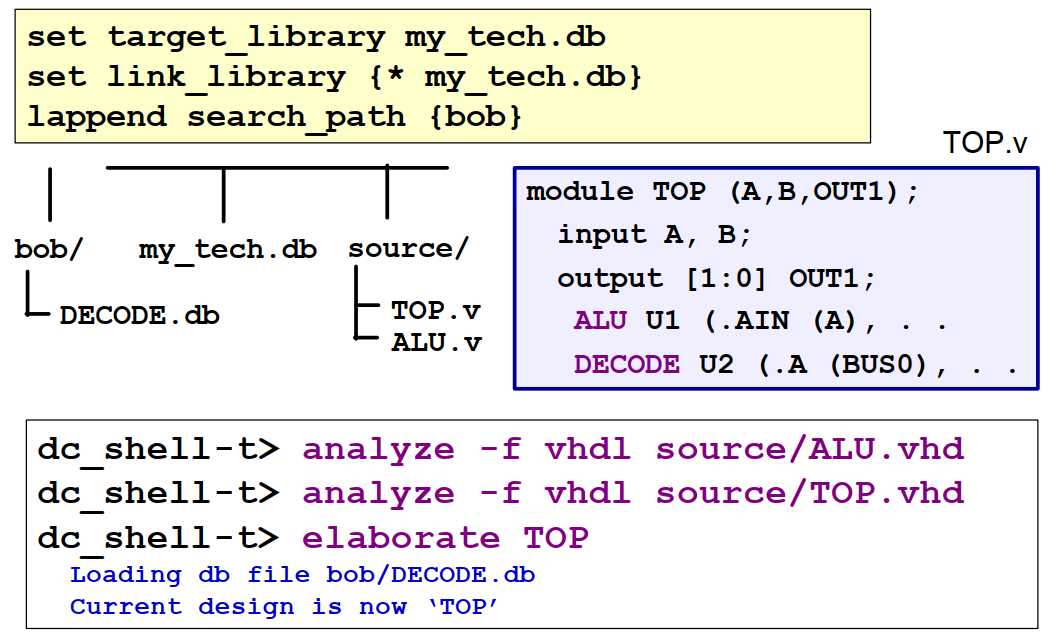

如何告诉DC在bob中找到DECODE.db ?

设置search_path变量

使用analyze/elaborate

标签:ops get setup 兼容 bsp 文本 模块 路径 pre

原文地址:https://www.cnblogs.com/streetlive/p/13377748.html