标签:cloc inf backbone ack strong 切换 不同 一点 buffers

FPGA的时钟资源介绍主要分为三部分。第一部分是区域结构,第二部分是元件功能,第三部分是实现方式。

首先FPGA的时钟资源负责驱动所有的时序逻辑,生产商尽力使得时钟资源充分,可靠,为了达成这一目的,xilinx采取了结构化的时钟资源布局方式。

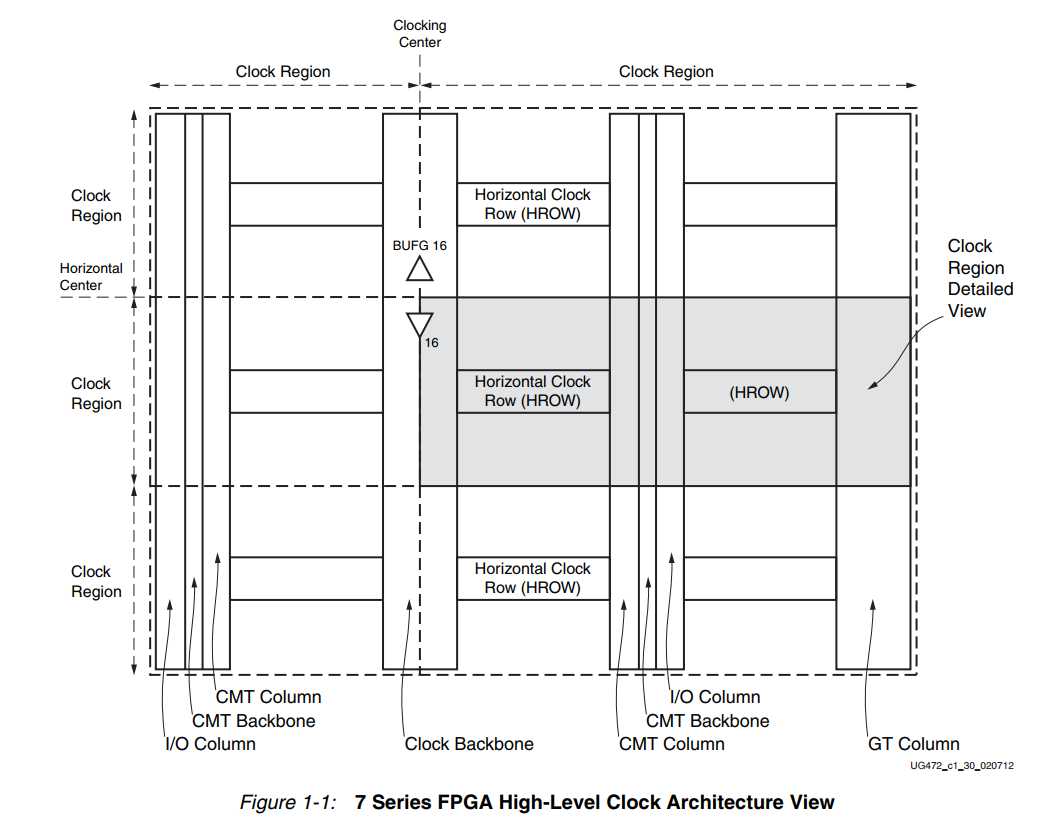

首先将整个板子分为左右两部分,宽度完全一致,中间是大动脉。也就是下图中的Clocking Center位置的Clocking Backbone,所有的BUFG(Global Clock buffers)也是包含在这里面。

顾名思义,BUFG是全局的Clock buffer。

BUFG能

1.作为时钟使能控制跨越了数个时钟域的时钟

2.作为无毛刺的多路复用器进行时钟二选一亦或是切换掉失效的时钟

3.被CMT驱动来消除时钟分发延迟,调整相对另一个时钟的延迟

以上是来自UG的翻译,不必深究,我们只需要知道它的驱动范围最广,分布位置在中间的大动脉里就行了。

一条动脉显然无法给整个人体供血,有限个数的BUFG也无法直接驱动所有的逻辑资源。虽然BUFG的驱动范围最广,但是所有资源都使用BUFG也不能获得最好的效果。(为什么?)

所以我们还需要横向的血管,也就是HROW(Horizontal Clock Row),它们等距水平分布,非常像模拟城市里建造道路时的棋盘式布局。但是HROW不同于Clock Backbone,它们主要负责相邻上下两个部分的时序逻辑资源驱动,具体实现则通过BUFH,BUFH相当于作用范围阉割版的BUFG。

在这里还要强调一点,所有的全局时钟信号线布线时都必须经过Clock Backbone,而当全局时钟信号线从Clock Backbone出来之后,要进入具体的时钟区域时,则必须通过HROW。那么我们可以这么总结,所有的全局时钟线布线时都必须经过Clock Backbone和HROW。

时钟区域是什么?时钟区域是板子的划分,它的上下界限在两条HROW的中间处,也就是说,每个时钟区域的中间都有一条HROW横穿而过。而它的左右界限则是两条CMT Backbone的中间处,同理,每个时钟区域的中间都有一条CMT Backbone竖穿过去。根据板子的大小不同,时钟域数量从1到24不等。一个时钟域包括了所有的同步组件(CLB, I/O, serial transceivers, DSP, block RAM, CMT)。每个时钟域包括了50个CLB和1个I/O bank(50 I/Os)。

在横向的血管之外,我们还需要小血管和毛细血管,对应BUFMR和BUFR。BUFMR可以驱动本时钟域内所有的时序资源以及上下相邻的两个时钟域。当它驱动相邻时钟域时,布线需要经过CMT Backbone。而BUFR只能驱动本时钟域内的时序资源。

而BUFIO只能驱动本时钟域内的I/O部件。

至此,基本的结构就介绍完了,除此之外还有I/O Column和GT column,我们稍后介绍。

标签:cloc inf backbone ack strong 切换 不同 一点 buffers

原文地址:https://www.cnblogs.com/aliothx/p/13398060.html