标签:样本 部分 ram 覆盖 成本 被锁 导致 制造业 环境

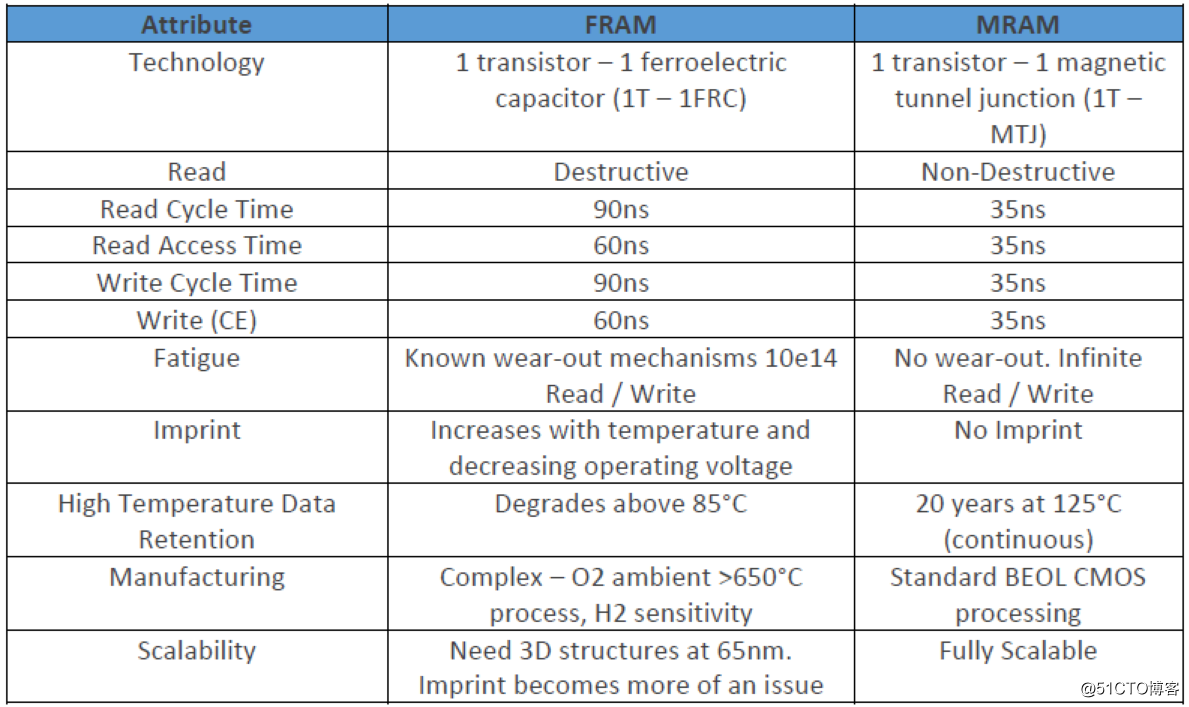

疲劳MRAM技术使用磁态进行数据存储。在两种状态之间切换磁极化不需要原子的运动,因此MRAM器件没有磨损机制。FRAM中的位存储需要响应电场,使其固有的电偶极子(在Pb(Zr,Ti)O3的情况下,氧八面体中的Ti4+离子)移动。随着时间的流逝,电容器中自由电荷的积累和其他离子缺陷将越来越阻碍偶极子的移动,此外与铁电偶极子的氢键键合是一种已知的磨损机制,这就是为什么CMOS中需要关注H2污染的原因BEOL制造FRAM。

保留/相反状态保留

FRAM技术在存储元件的磁滞行为中具有固有的不对称性。与顶部电极相比,底部电极具有更高的热收支,导致铁电元件的优选偶极子定向。随着时间的流逝,该优选取向最终将变得如此占主导地位,以至于外部编程电压将不再能够将偶极子重新取向出优选取向。存储单元被锁定为首选方向,从而导致存储位故障。

FRAM技术的另一个问题是响应较低的读取电压会降低极化(信号)。在写入操作期间将完整的电源电压施加到电容器,但是在读取操作期间,只有一部分电压会施加到铁电元件,因为读取电压在寄生电容和铁电电容之间分配。结果,在随后的读取中,状态之间的电压裕度减小,并最终导致无法区分状态。

高温数据保留

超过85°C的环境工作温度会加速FRAM的磨损,因为会积聚自由电荷,从而导致烙印。

Everspin MRAM在精心设计的实验中得到了证明,可以在125°C的温度下将数据保留长达20年。

扩展温度

扩展温度的FRAM(工业和汽车(AEC-Q1001级))通常需要使用2T-2FC体系结构。这种架构允许自参考读取,以补偿较高工作温度下的弱化极化(信号余量)。

Everspin MRAM不需要更改其他架构即可满足工业和汽车温度要求。

制造业

Everspin MRAM产品使用标准的商用CMOS制造技术制造。磁性元件建立在两个Cu金属层之间,通常是最后一个和倒数第二个金属层。除了在金属沟槽中添加磁性覆盖层之外,与标准BEOLCMOS工艺没有任何偏差。

FRAM产品集成在第一个BEOL金属层之前的W插头上。在FRAM工艺的高温下(沉积PZT膜需要650℃),W形插头容易氧化,因此缺陷控制成为一个挑战。

在返回标准BEOLCMOS处理之前,必须将铁电电容器封装在AlOx中,以防止H2扩散到其他铁电元件中。

可扩展性

在65纳米或更小的制造节点上,将需要3D架构来构建铁电(FRAM)元件。随着特征尺寸的减小,烙印或铁电偶极子的非优选取向的风险会增加。Everspin MRAM使用标准的CMOS技术,具有更大的可扩展性,同时功能尺寸减小,而成本却不高。

比较FRAM和MRAM(MR0A08A与FM28V100,2.7V至3.6V)

MRAM好处

源自浮栅技术的传统可写非易失性存储器使用电荷泵在芯片上产生高电压(10V或更高),以迫使载流子通过栅极氧化物。因此,存在长的写入延迟,高的写入功率,并且写入操作实际上对存储单元具有破坏性。浮动门设备无法支持超过10e6次访问的写操作。从一个角度来看,使用EEPROM以1个样本/秒的速度记录数据的数据记录器将在不到12天的时间内磨损。相比之下,Everspin MRAM产品几乎提供无限的耐用性(10e16次访问)。

标签:样本 部分 ram 覆盖 成本 被锁 导致 制造业 环境

原文地址:https://blog.51cto.com/14618340/2523322