标签:高性能 info 技术 html ams 字节 分享 时间 inf

XRAM是一种新的内存架构,旨在以具有竞争力的价格提供高密度和高性能RAM.XRAM使用先进的DRAM技术和自刷新架构来显着提高内存密度,性能并简化用户界面。XM8A51216V33A在功能上等效于异步SRAM,是一种高性能8Mbit CMOS存储器,组织为512K字乘16位和1024K字乘8位,支持异步SRAM存储器接口。

特征

?异步XRAM内存

?高速访问时间

?tAA=10/12纳秒

?低有功功率

?ICC=80 mA时为55 mA

?低CMOS待机电流

?ISB2=20 mA(典型值)

?工作电压范围:2.2 V至3.6 V

?取消选择时自动掉电

?TTL兼容的输入和输出

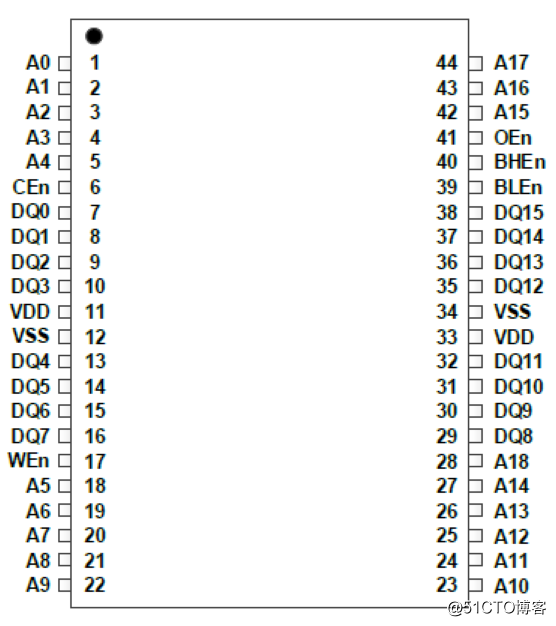

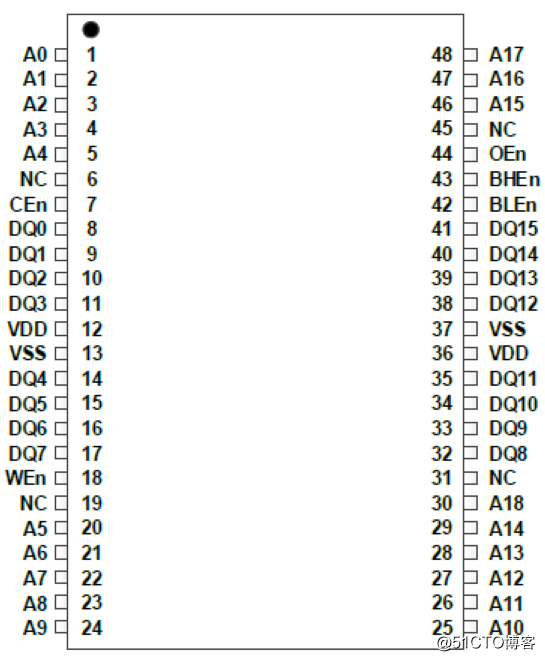

?提供44引脚TSOP II,48引脚TSOP I封装和48焊球FBGA封装

44引脚TSOP II引脚排列

48引脚TSOP I引脚排列

要写入设备,请将芯片使能(CE)和写使能(WE)输入设为低电平。如果字节低使能(BLE)为低,则来自I / O引脚(DQ0至DQ7)的数据被写入地址引脚(A0至A18)上指定的位置。如果字节高使能(BHE)为低电平,则来自I / O引脚(DQ8至DQ15)的数据将写入地址引脚(A0至A18)上指定的位置。要从器件读取,请将芯片使能(CE)和输出使能(OE)设为低电平,同时将写入使能(WE)设为高电平。如果字节低使能(BLE)为低,则地址引脚指定的存储器位置中的数据将出现在DQ0至DQ7上。如果字节高使能(BHE)为低,则来自存储器的数据出现在DQ8到DQ15上。

取消选择器件(CE),禁用输出(OE HIGH),禁用BHE和BLE(BHE,BLE HIGH)或以下操作时,输入或输出引脚(DQ0至DQ15)处于高阻抗状态写操作(CE和WE LOW)。突发模式引脚(MODE)定义突发序列的顺序。当置为高电平时,将选择交错的突发序列。当拉低时,选择线性突发序列。

分享一款国产异步SRAM 8Mb CMOS存储器XM8A51216V33A

标签:高性能 info 技术 html ams 字节 分享 时间 inf

原文地址:https://blog.51cto.com/14618340/2529568