标签:导致 电路 逻辑操作 png 不同 时序 实现 测试 解析

1、什么是时钟抖动(jitter)

芯片的某一个给定点上时钟周期发生暂时性变化,即达到电路某一点的连续时钟边沿之间间隔的变化称为时钟抖动。

2、什么是时钟偏移(skew)

时钟信号到达数字电路各个部分所用时间的差异。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了 skew。

二者区别:Jitter是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。Skew是由不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

3、FPGA中采用全局时钟网络的好处优点

(1)负载能力强,任何一个全局时钟线都可以驱动芯片内部的触发器。

(2)时延差特别小。

(3)时钟信号波形畸变小,工作可靠性好。

(4)对于一个设计项目来说,全局时钟是最简单和最可预测的时钟。

最好的时钟方案是:由专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。只要可能就尽量在设计项目中采用全局时钟。CPLD/FPGA都具有专门的全局时钟引脚。它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

同步设计时:全局时钟输入一般都接在器件的时钟端,否则会使其性能受到影响,对于需要多时钟的时序电路,最好选用一个频率是他们的时钟频率公倍数的高频主时钟。

4、FPGA对时钟的使用?

FPGA有固定的时钟路由,这些路由能有效减少时钟抖动和偏差。需要对时钟进行相位移动或变频的时候,一般不允许对时钟进行逻辑操作,这样不仅会增加时钟的偏差和抖动,还会使时钟带上毛刺。一般的处理方法是采用FPGA芯片自带的时钟管理器如PLL,DLL或DCM,或者把逻辑转换成触发器的D输入。

5、门控时钟由哪些作用?

(1)降低功耗;(2)节省面积;

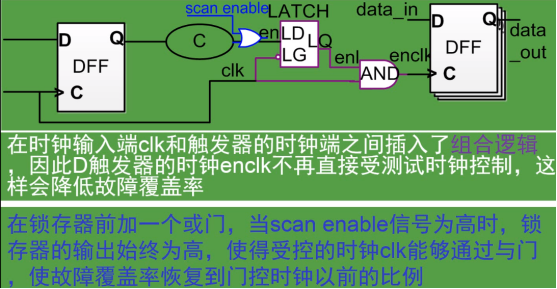

6、门控时钟导致电路测试覆盖率降低,如何解决?

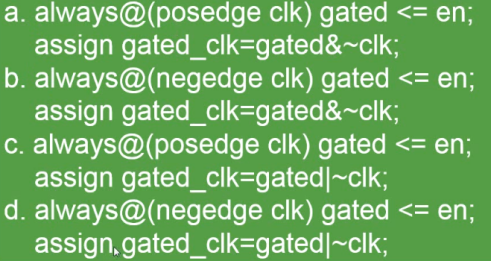

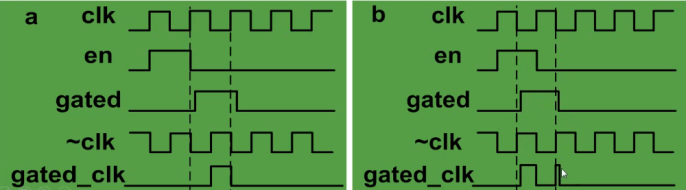

7、以下哪个电路会产生无毛刺的门控时钟?(a)

分析:ab选项的时序如下所示:c选项和b一样,d选项起不到门控的作用,因此选a。

8、以下哪个不属于PLL的组成部分(A)

A、Divid

B、voltage controlled

C、Phase detector

D、Loop Filter

解析:锁相环是由另外部分组成的

9、Xilinx的FPGA中,下列哪种片上资源可以实现时钟的分频和倍频(B)

A、BUFIO

B、MMCM

C、ODDR

D、BUFG

解析:三部分MMCM,DMM,PLL。

10、下面关于PLL电路表述正确的是:(BC)

A.PLL属于模拟电路,无法用全数字电路实现

B.PLL相对于参考时钟,可以输出分频、倍频、分数频的时钟

C.PLL输入的参考时钟jitter值,在PLL输出时会变大,也可能变小

D.PLL的jitter值等于同步数字电路中clock uncertainty的设定值

解析:A,PLL可以用数字电路实现;D,clock uncertainty包括jitter+skew

11、某移位寄存器的时钟脉冲频率是100KHZ,欲将存放在该寄存器中的数左移8位,完成该操作需要(C)时间。

A、80ms B、12.5ms C、80usD、10us

12、综合中的clock uncertainty以下哪些内容?(ABC)

A、PLL jitter

B、CTS后的clock skew

C、综合时加的margin

D、clock network latency

13、输入时钟频率 250Mhz,输入数据率8Gbps,输出的时钟频率 200Mhz,输出数据率为5Gbps,单位时间内输入数据总量为4Gb,在保证数据不丢失的前提下,最少需要多大的缓冲空间,并给出分析步骤。

单位时间内输入数据总量为4Gb,输入数据率为8Gbps,所用时间为0.5s,则输出数据总量为0.5*5=2.5Gb,缓冲空间=4Gb-2.5Gb=1.5Gb。

14、验证一个模块时,发现simulation hang住了,波形中clk不往前走了,最有可能是什么原因引起的?(D)

A、.DUT复位

B、 Testbench复位

C、时钟复位

D、进入了死循环

标签:导致 电路 逻辑操作 png 不同 时序 实现 测试 解析

原文地址:https://www.cnblogs.com/xianyufpga/p/13644313.html