标签:port 子模块 repo out output solution ops 成功 code

这里直接使用DC教程的lab1。

①首先在虚拟机中新建一个文件夹test,把lab1和ref这两个文件夹复制到test中。

②可以查看一下lab1的文件情况,因为有.开头的隐藏文件,所以命令:ls -a。

[IC@IC lab1]$ ls -a

. common_setup.tcl mapped scripts .synopsys_dc.setup work

.. dc_setup.tcl rtl .solutions unmapped

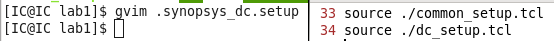

③修改.synopsys_dc.setup的内容,如下:

④修改common_setup.tcl的内容,修改之处红色部分,如下:

##########################################################################################

# User-defined variables for logical library setup in dc_setup.tcl

##########################################################################################

set ADDITIONAL_SEARCH_PATH "../ref/libs/mw_lib/sc/LM ./rtl ./scripts " ;# Directories containing logical libraries,

# logical design and script files.

set TARGET_LIBRARY_FILES sc_max.db ;# Logical technology library file

set SYMBOL_LIBRARY_FILES sc.sdb ;# Symbol library file

##########################################################################################

# User-defined variables for physical library setup in dc_setup.tcl

##########################################################################################

set MW_DESIGN_LIB TOP_LIB ;# User-defined Milkyway design library name

set MW_REFERENCE_LIB_DIRS ../ref/libs/mw_lib/sc ;# Milkyway reference libraries

set TECH_FILE ../ref/libs/tech/cb13_6m.tf ;# Milkyway technology file

set TLUPLUS_MAX_FILE ../ref/libs/tlup/cb13_6m_max.tluplus ;# Max TLUPlus file

set TLUPLUS_MIN_FILE ../ref/libs/tlup/cb13_6m_min.tluplus ;# Min TLUPlus file

set MAP_FILE ../ref/libs/tlup/cb13_6m.map ;# Mapping file for TLUplus

⑤可以打开dc_setup.tcl文件,但是内容不需要改动。命令:gvim dc_setup.tcl。

⑥图形化的形式启动DC,命令:design_vision -topo。

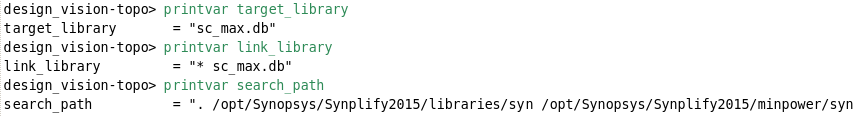

⑦分别输入三条命令检查库是否正确设置,如下:

⑧输入命令:check_library。检查逻辑库和物理库的一致性,结果发生这个问题:

Information: Logic library is INCONSISTENT with physical library (LIBCHK-220)

虽然两者不一致,但是可以忽略这个问题。

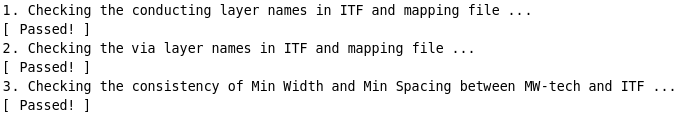

⑨输入命令:check_tlu_plus_files。检查寄生参数文件和工艺文件的一致性。

结果会有3个passed。

⑩读入设计文件,命令:read_file -format verilog ./rtl/TOP.v。

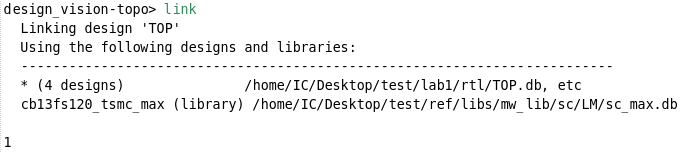

?查看当前要综合的设计是否缺少子模块,命令:link。

结果返回1,说明子模块完整。

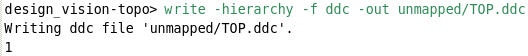

?以ddc的格式保存未映射的设计,文件保存到lab1文件夹中的unmapped中,命令:write -hierarchy -f ddc -out unmapped/TOP.ddc。

结果返回1,保存成功。

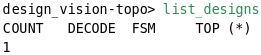

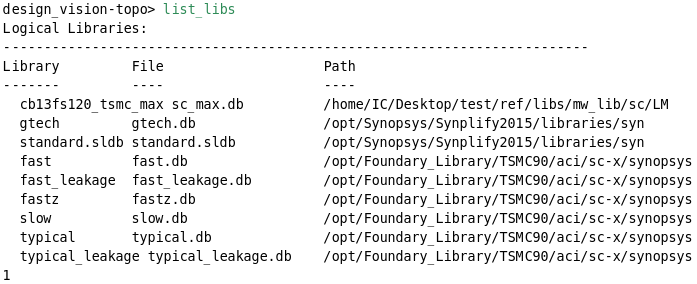

?查看内存中的设计和库,命令:list_designs 、 list_libs。

?进行综合,命令:compile_ultra。

查看是否违规,命令:report_constraint -all。

查看时序报告,命令:report_timing。

查看面积情况,命令:report_are。

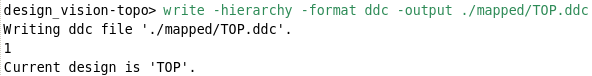

?保存综合后的设计,保存到mapped文件夹中,命令:write -hierarchy -format ddc -output ./mapped/TOP.ddc。

结果返回1,说明保存成功。

?学习的文章:https://www.cnblogs.com/IClearner/p/6618992.html

标签:port 子模块 repo out output solution ops 成功 code

原文地址:https://www.cnblogs.com/FPGAer/p/13771821.html