标签:bit pdf 过程 rom header stage app comm 比特流

ZYNQ SOC的FPGA引导由ARM完成,引导流程大致如下:Stage 0 (BootROM: BootROM Header) -> Stage 1 (FSBL / User code) -> Stage 2 (U-Boot / System / Application)。裸机时,stage2完成Fabric的引导以及ARM的引导。

完成引导程序ARM启动后,ARM可以通过bitstream.bit.bin重新引导Fabric。其中重点注意一下几点:

①首次引导时如果加载了Fabric,再次升级时,必须先初始化FPGA,然后再跟新bin文件。

②ARM更新Fabric用的文件不是.bit文件而是.bin文件,对于Vivado 2019.2可以由Vivado->Tool->General Memory configuration file工具生成,具体命令如下(命令解析详见《ug835-vivado-tcl-commands.pdf》):

write_cfgmem -format bin -size 16 -interface SMAPx32 -loadbit {up 0x00000000 "D:/20200623_Nemo/nemo_code/test/hdmi_v10/hdmi_cb/_ide/bitstream/nemo_plat_wrapper.bit" } -force -disablebitswap -file "D:/20200623_Nemo/nemo_code/test/hdmi_v10/hdmi_cb/_ide/bitstream/bit.bin"

具体代码就不贴出来了,vitis中有实验例程,但是要注意vitis中的例程没有初始化Fabric的过程,如果第一次加载时引导了Fabric,再次更新的bin文件无法正常执行。

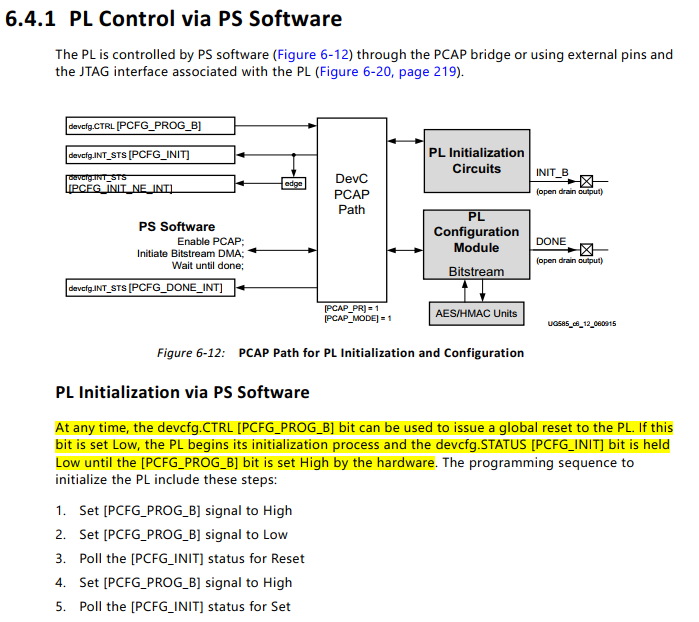

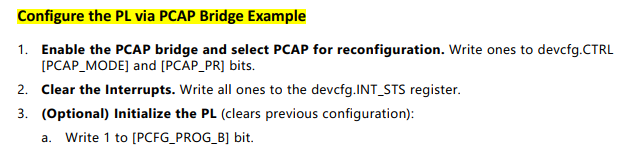

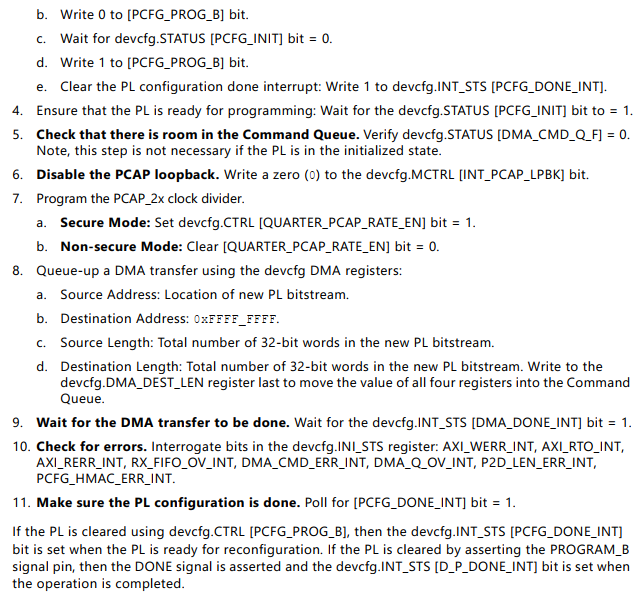

《ug585-zynq-7000-swr.pdf》文件中初始化PL和更新PL的流程如下:

ZYNQ 7000系列 - PS更新PL/FPGA/Fabric比特流bitstream

标签:bit pdf 过程 rom header stage app comm 比特流

原文地址:https://www.cnblogs.com/ivan0512/p/14150432.html