标签:action base tla 测试 rate state source interrupt 比较

一般工程的底层代码搭建好之后,大部分应用程序中用到的PWM功能可以用以下三个函数表示:

* 修改PWM占空比、周期

typedef struct{

Uint16 TBPRD7;

Uint16 TBPRD8;

Uint16 TBPRD9;

Uint16 TBPRD10;

Uint16 TBPRD11;

Uint16 TBPRD12;

Uint16 CmpA7;

Uint16 CmpA8;

Uint16 CmpA9;

Uint16 CmpA10;

Uint16 CmpA11;

Uint16 CmpA12;}

PwmData;

void PwmManage(PwmData*data){

EPwm7Regs.TBPRD = data->TBPRD7;

EPwm8Regs.TBPRD = data->TBPRD8;

EPwm9Regs.TBPRD = data->TBPRD9;

EPwm10Regs.TBPRD = data->TBPRD10;

EPwm11Regs.TBPRD = data->TBPRD11;

EPwm12Regs.TBPRD = data->TBPRD12;

EPwm7Regs.CMPA.bit.CMPA = data->CmpA7;

EPwm8Regs.CMPA.bit.CMPA = data->CmpA8;

EPwm9Regs.CMPA.bit.CMPA = data->CmpA9;

EPwm10Regs.CMPA.bit.CMPA = data->CmpA10;

EPwm11Regs.CMPA.bit.CMPA = data->CmpA11;

EPwm12Regs.CMPA.bit.CMPA = data->CmpA12;}

* 释放PWM

void PwmEnable(void){

EALLOW;

EPwm1Regs.TZCLR.bit.OST = 1;

EPwm2Regs.TZCLR.bit.OST = 1;

EPwm3Regs.TZCLR.bit.OST = 1;

EPwm4Regs.TZCLR.bit.OST = 1;

EPwm5Regs.TZCLR.bit.OST = 1;

EPwm6Regs.TZCLR.bit.OST = 1;

EPwm7Regs.TZCLR.bit.OST = 1;

EPwm8Regs.TZCLR.bit.OST = 1;

EPwm9Regs.TZCLR.bit.OST = 1;

EPwm10Regs.TZCLR.bit.OST = 1;

EPwm11Regs.TZCLR.bit.OST = 1;

EPwm12Regs.TZCLR.bit.OST = 1;

EDIS; }* 闭锁PWM

void PwmDisable(void){

EALLOW;

EPwm1Regs.TZFRC.bit.OST = 1;

EPwm2Regs.TZFRC.bit.OST = 1;

EPwm3Regs.TZFRC.bit.OST = 1;

EPwm4Regs.TZFRC.bit.OST = 1;

EPwm5Regs.TZFRC.bit.OST = 1;

EPwm6Regs.TZFRC.bit.OST = 1;

EPwm7Regs.TZFRC.bit.OST = 1;

EPwm8Regs.TZFRC.bit.OST = 1;

EPwm9Regs.TZFRC.bit.OST = 1;

EPwm10Regs.TZFRC.bit.OST = 1;

EPwm11Regs.TZFRC.bit.OST = 1;

EPwm12Regs.TZFRC.bit.OST = 1;

EDIS; }上面代码中释放与闭锁PWM的功能是由软件TRIP实现的。

以上三个函数基本在两电平或者三电平逆变器上用的比较多,除此之外PWM还有很多其他功能,接下来笔者慢慢列举。

PWM启动ADC

这是一个比较常用的功能,基本上如果使用DSP的片内ADC,大部分都会用PWM触发ADC,或者外部中断启动ADC。

PWM启动ADC,主要是考虑启动ADC的周期,常规的做法启动ADC转换的周期就是PWM的周期,这种做法适用于PWM周期比较长的情况下,如果PWM周期比较短,可能需要隔好几个PWM周期,再启动一次ADC转换。

//ADC SOC EPwm1Regs.ETSEL.bit.SOCAEN = 1;

// Enable SOC on A group

EPwm1Regs.ETSEL.bit.SOCASEL = 1;

// When TBCTR == 0x0000,EPWMxSOCA pulse will be //generated EPwm1Regs.ETPS.bit.SOCAPRD = 1;

// Generate pulse on 1st event* PWM触发中断

一般DSP系统中的主中断,都是ADC转换完成后触发的主中断,因为大部分的应用需求,都是希望DSP进入主中断后能够读取ADCRESULT,所以采用ADC触发的中断,一点都不浪费时间。

但有人认为ADC是个不稳定的东西,他们认为ADC转换过程中有机率出现问题,这种情况下,会导致系统无法进入主中断,而产生一系列问题?所以也有人用PWM的CMPB触发的中断作为主中断,但CMPB要在ADC转换完成之后才能触发中断,,这是为了进入主中断后读取的ADCRESULT,是当前周期转换的,而不是上个周期的。

EPwm1Regs.ETSEL.bit.INTSEL = 6; // time-base counter equal to //CMPB when the timer //is incrementin EPwm1Regs.ETPS.bit.INTPRD = 1; // Generate interrupt on 1st event EPwm1Regs.CMPB = 1000;

* PWM的TRIP模块

TRIP这个词,不好翻译,暂时还是用英文吧,笔者也没有看过特别合适的中文翻译,PWM的TRIP模块,主要功能是关系到PWM的释放与闭锁,闭锁一般是使PWM的A、B 引脚输出低电平。

然后TRIP分为硬件TRIP、软件TRIP,这两者实现的功能是相同的,只是触发TRIP事件的源头不同。硬件TRIP事件是怎么产生的,把DSP的一个GPIO设置为TRIP引脚,当该引脚的电平被拉低时,立即产生TRIP事件,此时PWM即会被闭锁。硬件TRIP闭锁PWM的速度很快,软件闭锁,可能至少需要几十us或者一个中断周期才能够闭锁PWM。

软件TRIP就是实现人为的闭锁、释放PWM功能。

EPwm1Regs.TZSEL.bit.OSHT1 = 1; // one-shit

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; //Force EPWMxA to a low state

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // Force EPWMxB to a low state

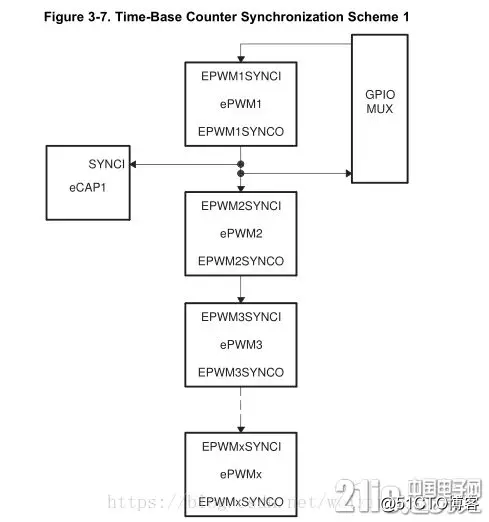

* PWM的脉冲同步性

PWM的同步性,主要是针对各个PWM模块而说的,比如PWM1与PWM12模块,希望这两个PWM模块的脉冲能够同步,这里同步就是指两者的波形能够重合,没有us级的差别。

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // Sync down-stream module

* PWM的引脚输出模式

一个PWM模块有PWM_A引脚,也有PWM_B引脚,这两个引脚的输出模式可以设置为互补模式,也可以设置为独立模式。

//独立模式

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; //大于比较值为0,小于比较值为1

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_DISABLE; //互补模式

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; //大于比较值为0,小于比较值为1

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBD = AQ_NO_ACTION;

EPwm1Regs.AQCTLB.bit.CBU = AQ_NO_ACTION;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

* PWM的相位

不同PWM模块之间的相位,可以同步,也可以相互错开,这种模式笔者测试过,还没有正式在项目中使用过,这种模式的设置应该和PWM的相位寄存器设置有关。

* PWM的死区

// Active Low PWMs - Setup Deadband

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //DB_ACTV_HIC

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL; //EPWMxA In (from the action-qualifier) is the //source for both falling-edge and rising-edge delay EPwm1Regs.DBRED = 400; EPwm1Regs.DBFED = 400; // TBCLK = SYSCLK 5.00 μSTi的C28x系列的DSP(28069)(28377D)PWM经验

标签:action base tla 测试 rate state source interrupt 比较

原文地址:https://blog.51cto.com/15057820/2566518