标签:style blog http color os sp div on 2014

module sync_module ( CLK, RSTn, VSYNC_Sig, HSYNC_Sig, Ready_Sig, Column_Addr_Sig, Row_Addr_Sig ); input CLK; input RSTn; output VSYNC_Sig; output HSYNC_Sig; output Ready_Sig; output [10:0]Column_Addr_Sig; output [10:0]Row_Addr_Sig; /********************************/ reg [10:0]Count_H; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count_H <= 11‘d0; else if( Count_H == 11‘d1056 ) Count_H <= 11‘d0; else Count_H <= Count_H + 1‘b1; /********************************/ reg [10:0]Count_V; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count_V <= 11‘d0; else if( Count_V == 11‘d628 ) Count_V <= 11‘d0; else if( Count_H == 11‘d1056 ) Count_V <= Count_V + 1‘b1; /********************************/ reg isReady; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) isReady <= 1‘b0; else if( ( Count_H >= 11‘d216 && Count_H < 11‘d1017 ) && ( Count_V >= 11‘d27 && Count_V < 11‘d627 ) ) isReady <= 1‘b1; else isReady <= 1‘b0; /*********************************/ assign VSYNC_Sig = ( Count_V <= 11‘d4 ) ? 1‘b0 : 1‘b1; assign HSYNC_Sig = ( Count_H <= 11‘d128 ) ? 1‘b0 : 1‘b1; assign Ready_Sig = isReady; /********************************/ assign Column_Addr_Sig = isReady ? Count_H - 11‘d216 : 11‘d0; // Count from 0; assign Row_Addr_Sig = isReady ? Count_V - 11‘d27 : 11‘d0; // Count from 0; /********************************/ endmodule

module vga_control_module ( CLK, RSTn, Ready_Sig, Column_Addr_Sig, Row_Addr_Sig, Red_Rom_Data, Green_Rom_Data, Blue_Rom_Data, Rom_Addr, Red_Sig, Green_Sig, Blue_Sig ); input CLK; input RSTn; input Ready_Sig; input [10:0]Column_Addr_Sig; input [10:0]Row_Addr_Sig; input [63:0]Red_Rom_Data; input [63:0]Green_Rom_Data; input [63:0]Blue_Rom_Data; output [5:0]Rom_Addr; output Red_Sig; output Green_Sig; output Blue_Sig; /**********************************/ reg [5:0]m; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) m <= 6‘d0; else if( Ready_Sig && Row_Addr_Sig < 64 ) m <= Row_Addr_Sig[5:0]; else m <= 6‘d0; reg [5:0]n; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) n <= 6‘d0; else if( Ready_Sig && Column_Addr_Sig < 64 ) n <= Column_Addr_Sig[5:0]; else n <= 6‘d0; /************************************/ assign Rom_Addr = m; assign Red_Sig = Ready_Sig ? Red_Rom_Data[ 6‘d63 - n ] : 1‘b0; assign Green_Sig = Ready_Sig ? Green_Rom_Data[ 6‘d63 - n ] : 1‘b0; assign Blue_Sig = Ready_Sig ? Blue_Rom_Data[ 6‘d63 - n ] : 1‘b0; /***********************************/ endmodule

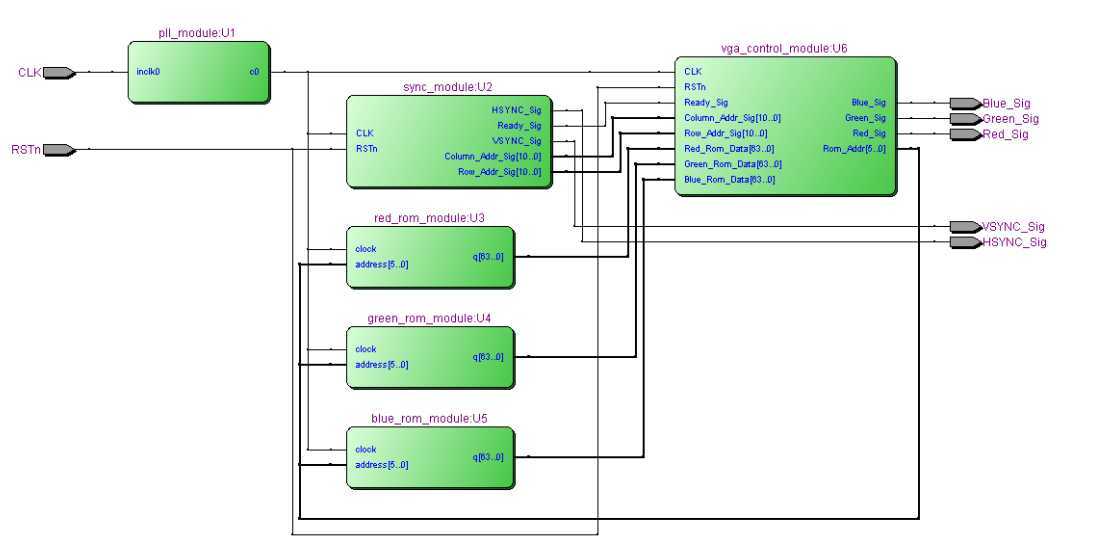

module vga_module ( CLK, RSTn, VSYNC_Sig, HSYNC_Sig, Red_Sig, Green_Sig, Blue_Sig ); input CLK; input RSTn; output VSYNC_Sig; output HSYNC_Sig; output Red_Sig; output Green_Sig; output Blue_Sig; /*************************************/ wire CLK_40Mhz; pll_module U1 ( .inclk0( CLK ), // input - from top .c0( CLK_40Mhz ) // output - inter globak ); /**************************************/ wire [10:0]Column_Addr_Sig; wire [10:0]Row_Addr_Sig; wire Ready_Sig; sync_module U2 ( .CLK( CLK_40Mhz ), .RSTn( RSTn ), .VSYNC_Sig( VSYNC_Sig ), // input - from top .HSYNC_Sig( HSYNC_Sig ), // input - from top .Column_Addr_Sig( Column_Addr_Sig ), // output - to U6 .Row_Addr_Sig( Row_Addr_Sig ), // output - to U6 .Ready_Sig( Ready_Sig ) // output - to U6 ); /******************************************/ wire [63:0]Red_Rom_Data; red_rom_module U3 ( .clock( CLK_40Mhz ), .address( Rom_Addr ), // input - from U6 .q( Red_Rom_Data ) // output - to U6 ); /******************************************/ wire [63:0]Green_Rom_Data; green_rom_module U4 ( .clock( CLK_40Mhz ), .address( Rom_Addr ), // input - from U6 .q( Green_Rom_Data ) // output - to U6 ); /******************************************/ wire [63:0]Blue_Rom_Data; blue_rom_module U5 ( .clock( CLK_40Mhz ), .address( Rom_Addr ), // input - from U6 .q( Blue_Rom_Data ) // output - to U6 ); /******************************************/ wire [5:0]Rom_Addr; vga_control_module U6 ( .CLK( CLK_40Mhz ), .RSTn( RSTn ), .Ready_Sig( Ready_Sig ), // input - from U2 .Column_Addr_Sig( Column_Addr_Sig ), // input - from U2 .Row_Addr_Sig( Row_Addr_Sig ), // input - from U2 .Red_Rom_Data( Red_Rom_Data ), // input - from U3 .Green_Rom_Data( Green_Rom_Data ), // input - from U4 .Blue_Rom_Data( Blue_Rom_Data ), // input - from U5 .Rom_Addr( Rom_Addr ), // output - to U3, U4, U5 .Red_Sig( Red_Sig ), // output - to top .Green_Sig( Green_Sig ), // output - to top .Blue_Sig( Blue_Sig ) // output - to top ); /*******************************************/ endmodule

标签:style blog http color os sp div on 2014

原文地址:http://www.cnblogs.com/shaogang/p/4094528.html