标签:简化 lan 处理 https 基本 load 插入 不能 detail

有点小激动,今天好像发现了新大陆。不知道讲的对不对,姑且记录一波,有不对的地方大家请指正。

在FPGA中,流水线技术就是向组合逻辑中插入寄存器,提升系统的时钟频率。

参考:FPGA流水线的详细解析

参考:系统架构之流水线技术

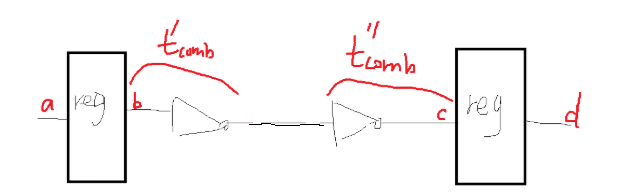

在一个简单的例子中,如下图。a到b节点的时间为clock,c到d节点的时间为clock。

而b到c的理想时间为0,但实际上由图中组合逻辑的延时,b到c有一定的延迟$t_{comb}$

那么此时一定有$t_{comb}+t_{set\_up} \le t_{clock} $,其中等于是比较极限的情况。

那么当组合逻辑过长,延迟过大,导致$t_{comb}+t_{set\_up} > t_{clock} $,甚至$t_{comb} > t_{clock} $ ,那么这个时候后级寄存器建立时间不能保证,,电路可能会产生亚稳态导致系统不稳定。

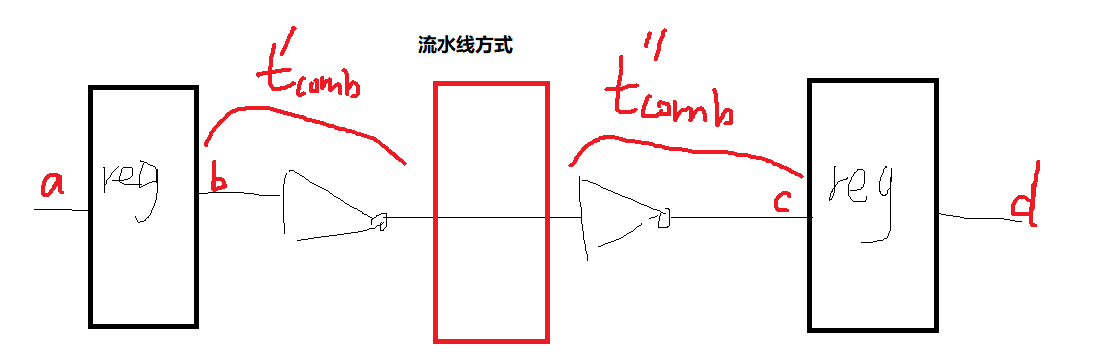

为了解决这种情况,有三种思路:1、增加$t_{clock}$,即降低系统频率 2、降低$t_{set\_up}$,这和工艺相关,暂不考虑 3、降低$t_{comb}$,这就需要对较长的组合逻辑进行拆分,插入寄存器,如下图的流水线方式。

参考:流水线技术

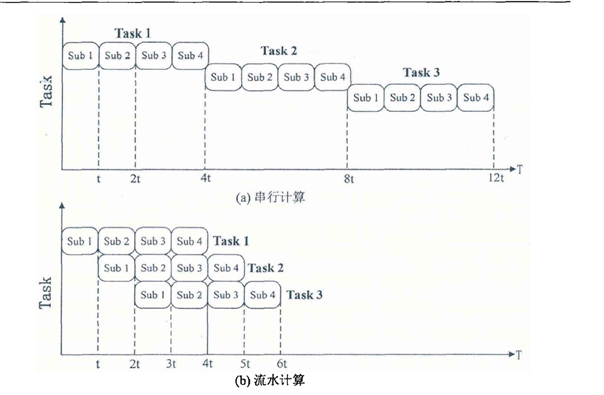

图中每条task为一条指令,假设所有的sub1-sub4代表的是取指、译码、访存、写回(仅仅就是个意思)

在串行方式的下:取指、译码、访存、写回为一个长的组合过程,因而一次只能执行一条指令此时的延时较大,因为组合逻辑很长。

在流水线的情况下:第一条指令在取指后,在下一个时钟周期第一条指令进行译码操作,同时第二条指令进行取指操作(不一定是一个时钟周期,这里是为了理解而进行的简化),

流水线方式能这样进行操作是因为在执行一条命令的四个过程中每个过程中间都会有一个寄存器来对上过程的结果进行寄存。

因而在在系统使用译码部件module(第一条指令使用)的时候,系统同时在使用取指部件module(第二条指令),两个部件可以同时进行工作,这不是纯组合逻辑能实现的。

在流水线的这一处理过程中,既体现了流水线,又体现了操作并行(不同部件同时工作),体现了流水线的优势和对电路稳定性的影响。

tips:这里的取指、译码、访存、写回只是为了形象的表示。真正地计算机中的执行指令的过程为 取指、译码、执行、访存、写回五个基本过程

此外,在这里的表述中指令执行的几个过程被默认为一个clock,但是这样解释是有一些bug,但是这样对流水线技术的理解方向不会产生很大影响。

标签:简化 lan 处理 https 基本 load 插入 不能 detail

原文地址:https://www.cnblogs.com/tianyuzh/p/14606759.html