标签:负载 term lib 混合 com 活动 变化 离线 混合应用

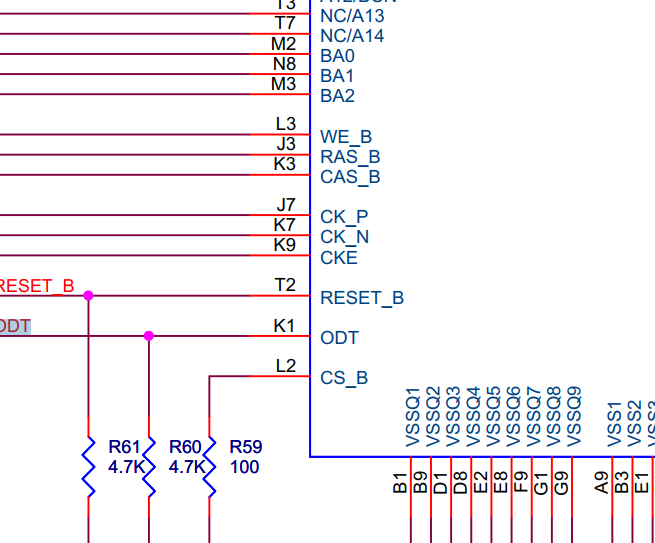

ODT ( On-DieTermination ,片内终结)

ODT 也是 DDR2 相对于 DDR1 的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸

收掉,而不会在电路上形成反射, 造成对后面信号的影响。 顾名思义, ODT 就是将端接电阻移植

到了芯片内部,主板上不再有端接电路。在进入DDR 时代, DDR 内存对工作环境提出更高的要求,如

果先前发出的信号不能被电路终端完全吸收掉而在电路上形成反射现象, 就会对后面信号的影响造成

运算出错。因此目前支持DDR主板都是通过采用终结电阻来解决这个问题。 由于每根数据线至少需要

一个终结电阻, 这意味着每块DDR 主板需要大量的终结电阻, 这也无形中增加了主板的生产成本 ,

而且由于不同的内存模组对终结电阻的要求不可能完全一样,也造成了所谓的“内存兼容性问题”。

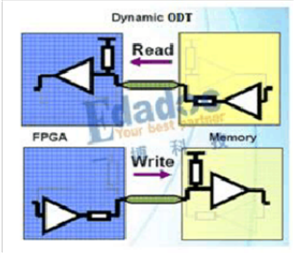

而在DDR-II 中加入了 ODT功能,当在DRAM 模组工作时把终结电阻器关掉, 而对于不工作的 DRAM 模

组则进行终结操作,起到减少信号反射的作用,如下图二所示。ODT 的功能与禁止由主控芯片控制,

在开机进行 EMRS 时进行设置, ODT 所终结的信号包括 DQS 、DQS# 、DQ 、DM 等。这样可以产生

更干净的信号品质,从而产生更高的内存时钟频率速度。而将终结电阻设计在内存芯片之上还可以简

化主板的设计,降低了主板的成本, 而且终结电阻器可以和内存颗粒的“特性”相符, 从而减少内

存与主板的兼容问题的出现

图二 0DT端接示意图

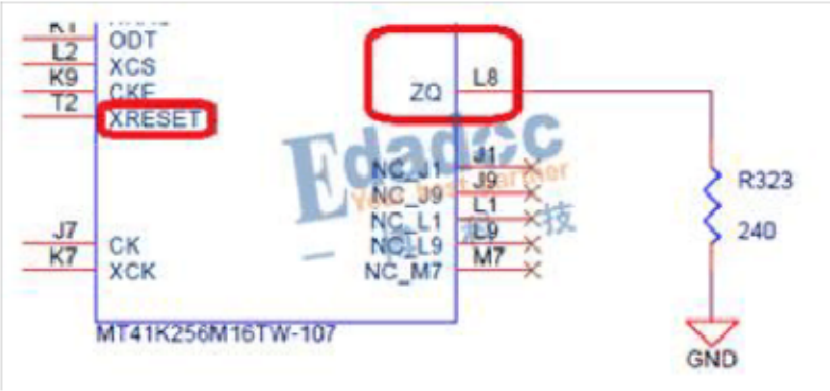

ZQ 校准

如下图三所示, ZQ 是DDR3一个新增的引脚,在这个引脚上接有一个 240 欧姆的低公差参考电阻。

这个引脚通过一个命令集,通过片上校准引擎( ODCE ,On-DieCalibrationEngine )来自动校

验数据输出驱动器导通电阻与 ODT 的终结电阻值。 当系统发出这一指令之后, 将用相应的时

钟周期 (在加电与初始化之后用 512 个时钟周期,在退出自刷新操作后用 256 时钟周期、在

其他情况下用 64个时钟周期)对导通电阻和 ODT 电阻进行重新校准。

ODT是终端匹配,那就是要在你的信号线终端上拉一个电阻,但是这个内部电阻随着温度会

有些细微的变化,为了保证信号被准确的进行终端匹配,就需要ZQ了,ZQ的作用就是使用你外面

连接的,高精度240R电阻来对这个内部的电阻进行校准,

图三 Reset 及 ZQ 引脚

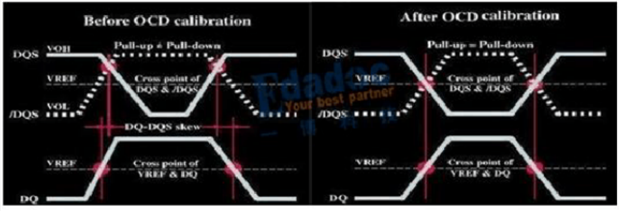

外驱动调校 OCD ( Off-ChipDriver )

OCD 是在 DDR-II 开始加入的新功能,而且这个功能是可选的,有的资料上面又叫离线驱动

调整。 OCD的主要作用在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值, 从而调整

DQS 与 DQ 之间的同步确保信号的完整与可靠性。 调校期间,分别测试 DQS 高电平和 DQ

高电平,以及 DQS 低电平和 DQ 高电平的同步情况。 如果不满足要求,则通过设定突发长

度的地址线来传送上拉 / 下拉电阻等级(加一档或减一档),直到测试合格才退出 OCD 操作,

通过 OCD 操作来减少 DQ 、 DQS的倾斜从而提高信号的完整性及控制电压来提高信号品质。

具体调校如下图一所示。

不过,由于在一般情况下对应用环境稳定程度要求并不太高,只要存在差分 DQS时就基本可以

保证同步的准确性, 而且 OCD 的调整对其他操作也有一定影响, 因此 OCD 功能在普通台式

机上并没有什么作用,其优点主要体现在对数据完整性非常敏感的服务器等高端产品领域。

图一 OCD

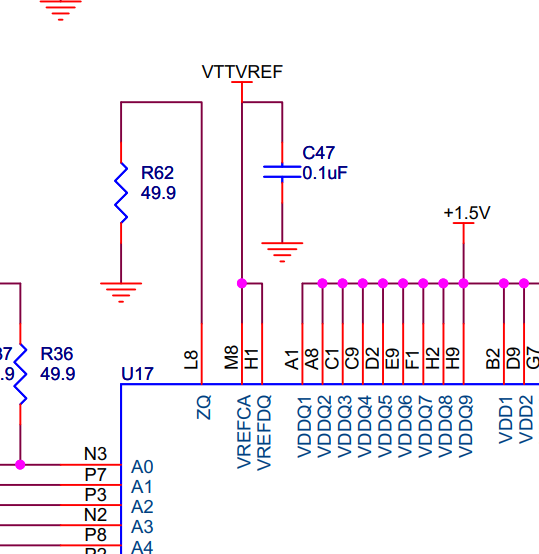

VREFCA & VREFDQ

对于内存系统工作非常重要的参考电压信号VREF,在DDR3系统中将VREF分为两个信号。一个是为

命令与地址信号服务的VREFCA,另一个是为数据总线服务的VREFDQ,它将有效的提高系统数据总

线的信噪等级,如下图四所示。

图4

重置(Reset)

重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。这一引脚将使DDR3的初始化处理变得简单。

当Reset命令有效时,DDR3 内存将停止所有的操作,并切换至最少量活动的状态,以节约电力。在Reset期间,

DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,且所有内部的程序装置将复位,

DLL(延迟锁相环路)与时钟电路将停止工作,甚至不理睬数据总线上的任何动静。这样一来,该功能将

使DDR3达到最节省电力的目的,新增的引脚如下图三所示。

Data Mask(DM)

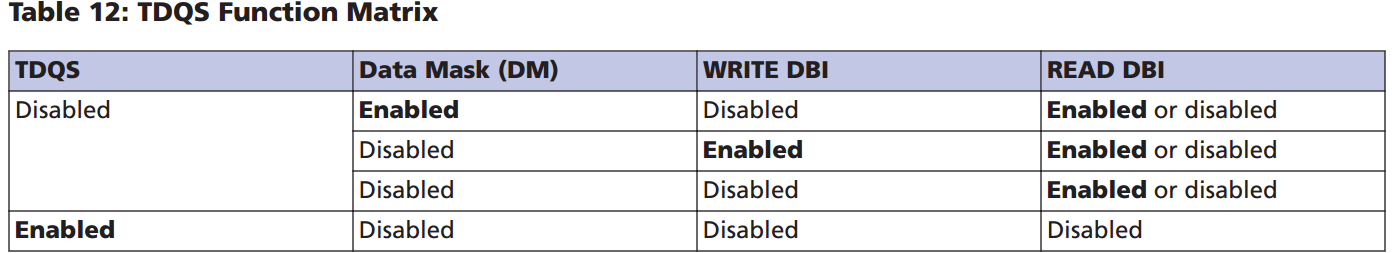

数据掩膜功能也称为部分写。只支持x8和x16配置。DM功能与DBI和TDQS功能共用相同的管脚。DM功能只用于写操作,且不能与写DBI功能同时使能。

应该说TDQS功能的优先级最高,如果使能了TDQS那么DM和DBI功能都被禁止

如果禁止了TDQS功能,才允许DM和DBI发挥作用。但有点我不太明白,DBI好像没有和TDQS及DM共用管脚啊

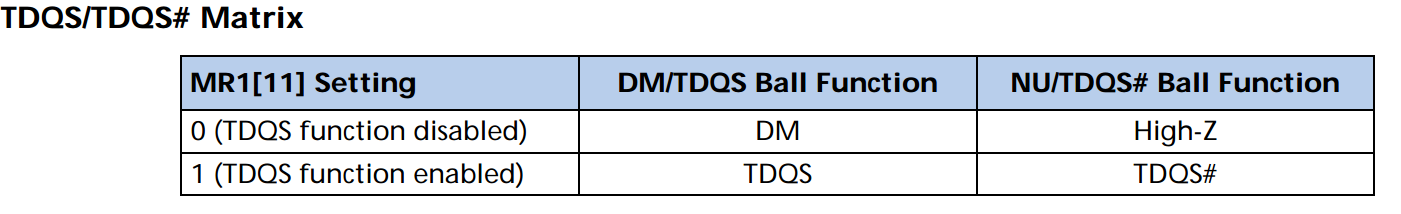

终端数据选通Termination Data Strobe (TDQS)

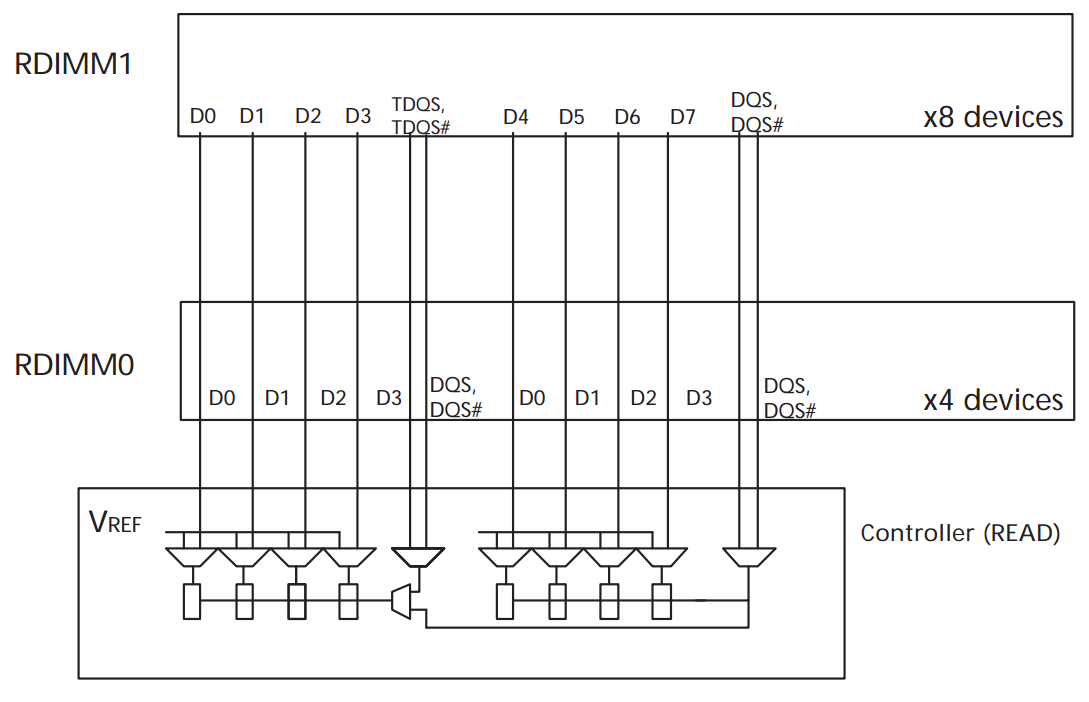

对于x8的DIMMs,每一个8位字节需要一个DQ选通道对(DQS/DQS#);对于x4的DIMMs,第半个

字节需要一对DQ选通对(DQS/DQS#)。当这两种不同的DIMM混合应用在同一个系统时,DQS

的负载就会不同,这样会造成信号完整性问题。TDQS就是为了解决这个问题的。

TDQS只用于x8 DRAM,不过TDQS还会和DM共同用用DM功能。

RDIMM0是x4 DRAM, RDIMM1是x8 DRAM, 由x4组成的RDIMM需要两个DQ选通对,其中一对连

接到x8的RDIMM1上实现同样的功能,另一个选通对对于RDIMM1是没有用处的,但是连接到了

TDSQ对上,当使能TDQS后,可以保证所有的选通脚负载一样。这样保证了信号的完整性。

ZQ校准

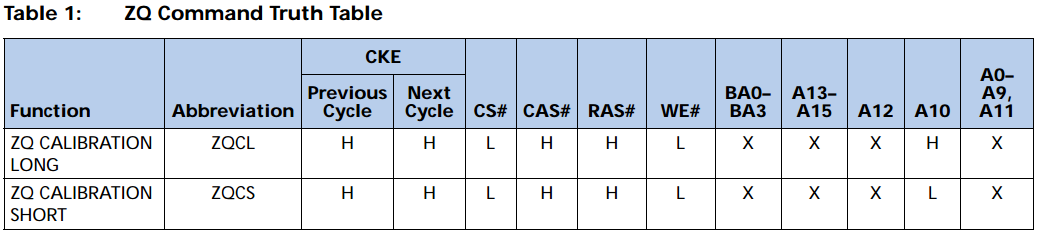

关于ZQ校正有两个命令ZQCL (ZQ CALIBRATION LONG )和ZQ CALIBRATION SHORT (ZQCS)

ZQCL主要用于系统上电初始化和器件复位,一次完整的ZQCL需要512个时钟周期,在随后(初始化和复位之后),校准一次的时间要减少到256周期。

ZQCS在正常操作时跟踪连续的电压和温度变化,ZQCS需要64个时钟周期。

ZQ 校准时序

在RESET之后的第一次ZQCL必须要512个时钟(tZQINIT)周期进行一次完整的校准。在之后 ZQCL 必须要tZQOPER(256个时钟周期)

ZQCS命令在除了ATCIVITIES的任何时间发送,

所有的BANK必须Precharged 并要满足tRP的时间要求,

标签:负载 term lib 混合 com 活动 变化 离线 混合应用

原文地址:https://www.cnblogs.com/jason20/p/14713384.html