标签:each 世界 信号 logic 创建 实例 变量类型 返回 技术

类class 对象oject

类是将相同的个体抽象出来的描述方式,对象是实体。

面向对象的三要素:封装,集成,多态

类的定义核心即使属性的声明和方法定义。

在验证的世界:

激励生成器:生成激励的内容

驱动器:将激励以时序的形式发送到DUT

检测器:检测信号并且记录

比较器:比较数据

验证环境的不同组件其功能和所需要处理的数据内容不同

第一个激励数据类:

class Transaction;

bit[31:0]addr,crc,data[8];

function void display;

$display("Transaction:%h",addr);

endfunction:dispaly

endclass:Transaction

class中的变量的生命周期是动态的,软件的变量。

bit[31:0]addr,crc,data[8];//默认的是变量类型

class属于硬件的世界,不能定义为reg变量

接口interface(软硬界的媒介)的指针可以传播到类class中

class中可以定义方法,在module定义的方法在initial always调用

class中不能够出现initial always ,但是class中定义的方法可以通过调用class来搞

Handle句柄,:指针,用来只想对象的指针。

句柄是指向对象的指针。

class中可以使用task和function

verilog的例化和SV的class的例化的差别:

两者的共同点在于使用相同的末班来创建内存实例

不同点在于verilog的例化是静态的,在编译连接时完成,而SVclass的例化是动态的,可以在任意的时间点发生,这使得类的例化方式更加灵活和空间

Verilog没有句柄,只能通过曾思华的索引

SVclass通过句柄可以将对象的指针赋予其他的句柄,使得操作更加的灵活

声明对象不同于创建(例化)

Transaction tr;//声明句柄

tr = new;//创建对象

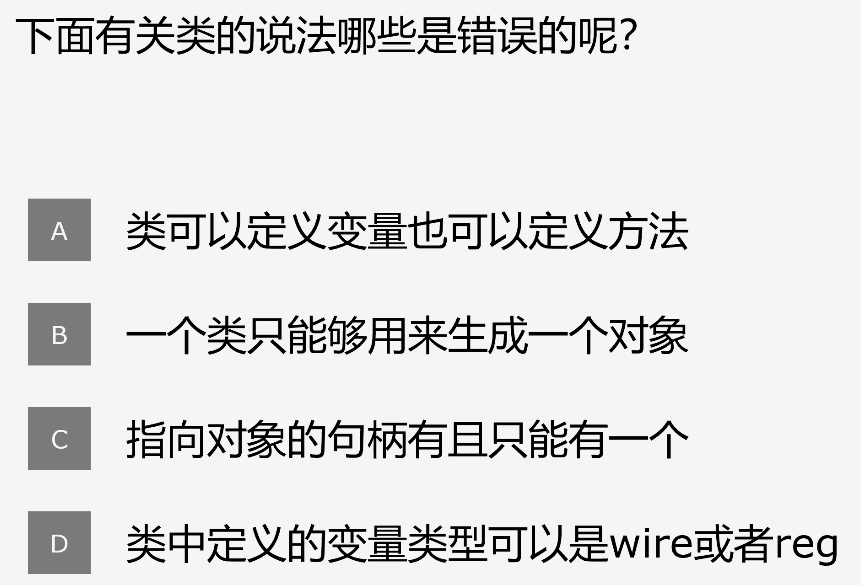

A:类是可以定义变量和方法的

B:一个类不仅仅能够用来生成一个对象

C:指向对象的句柄可以有很多个

D:类中不能够定义reg

创建对象:开辟了新的内存空间,用来存放新的成员变量和方法。

创建对象时候可以通过自定义构建函数,来完成变量的初始化和其他的初始化操作。

任何一个类class都需要new函数:

new()是系统预定义的函数,不需要指定返回值,函数会隐式的返回例化后的对象指针(句柄)。

class Transaction;

logic[31:0]addr,crc,data[8];

function new( );

addr = 3;

foreach(data[i])

data[i] = 5;

endfunction

endclass

国建函数也可以定义多个参数作为初始化时外部传入数值的手段。

class Transaction;

logic[31:0]addr = ‘h10;

logic[31:0]crc,data[8];

function new(logic[31:0] a=3,d=5);

标签:each 世界 信号 logic 创建 实例 变量类型 返回 技术

原文地址:https://www.cnblogs.com/justkeen/p/14839281.html