标签:tool 命名 asi rgba 说明 物理 puts 帮助文档 mic

Tcl(读Tickle) 全称(Tool Command Language),是一种简单易学又十分强大的脚本语言,在数字集成电路设计中应用十分广泛。

利用Tcl建立工程,配置相关芯片信号、设置工程路径、建立工程名称相关工程的基本参数,一键完成新工程使用。

#设置器件型号

set device_model xc7z035fbg676-2

#设置工程创建路径

set dev_dir {G:\DeskTop\ZynqCode\11_Tcl_test}

#切换到工程路径

cd $dev_dir

#显示工程路径

puts "The home_dir is $dev_dir now!"

#工程名称

set project_name tlc_test

#创建工程

create_project $project_name $dev_dir -part $device_model

#设置仿真语言为 verilog

set_property simulator_language Verilog [current_project]

利用Tcl脚本将工程所需要的文件添加进入工程。减少手动添加过程。

# 添加仿真tb文件

add_files -fileset sim_1 ./Sources/hdl/cpu_tb.v

# 添加VHDL文件

add_files [ glob ./Sources/hdl/bftLib/*.vhdl ]

add_files ./Sources/hdl/bft.vhdl

# 添加verilog文件

add_files [ glob ./Sources/hdl/*.v ]

add_files [ glob ./Sources/hdl/mgt/*.v ]

add_files [ glob ./Sources/hdl/or1200/*.v ]

add_files [ glob ./Sources/hdl/usbf/*.v ]

add_files [ glob ./Sources/hdl/wb_conmax/*.v ]

# 添加约束文件

add_files -fileset constrs_1 ./Sources/top_full.xdc

set_property library bftLib [ get_files [ glob ./Sources/hdl/bftLib/*.vhdl ]]

Tcl脚本在Vivado软件还可以自定义初始化脚本,添加图标,这样软件可以通过点击图标自动运行脚本,非常方便。zynq内嵌了ARM核和FPGA,在工程设计中添加ARM核应该是最常用的操作,因此这里就用添加ARM核作为初始化脚本功能来进行示例。

首先建立一个Tcl脚本,脚本大致内容为:

1.生成 block design;

2.添加 “processing_system7” IP 核;

3.配置使用的DDR 型号为"MT41J256M16 RE-125"

1 # 生成block design,命名为“design_1”

2 create_bd_design "design_1"

3 # 编译文件 sources_1

4 update_compile_order -fileset sources_1

5 # 生成zynq ps的IP核

6 startgroup

7 create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0

8 endgroup

9 # 配置IP核所用的DDR为“MT41J256M16 RE-125”

10 set_property -dict [list CONFIG.PCW_UIPARAM_DDR_PARTNO {MT41J256M16 RE-125} CONFIG.PCW_UART1_PERIPHERAL_ENABLE {1}] [get_bd_cells processing_system7_0]

通过vivado 的Tools -> Custom Commands -> Customize Commands,进行配置。

进入配置命令页面:

1.左侧"+" ,添加命令的名称;

2.右侧录入描述,在Source Tcl file 中添加刚才写好的脚本路径;

3.命令可以自己上传图片作为命令的工具栏图标。勾选 “Add to the toolbar”,选择我们的图标,点击"Apply"便完成了一键配置添加、配置PS核的脚本操作。

由于是在软件中自定义的命令操作,因此重新建立工程也无须重新配置。使用vivado软件时,将通用、重复软件操作配置为命令,在工具栏一键自动完成操作,将大大节省时间,提高工作效率。

下面是刚才建立的Command的相关演示。

把help 单独立一小节是因为在使用Tcl脚本的过程中,偶尔会忘记脚本使用或者命令名称等。这就需要常常使用Vivado 自带的Tcl help 功能。类似matlab一样,help相关命令会显示相关命令的使用方法、变量参数等,实在是很方便也很重要。

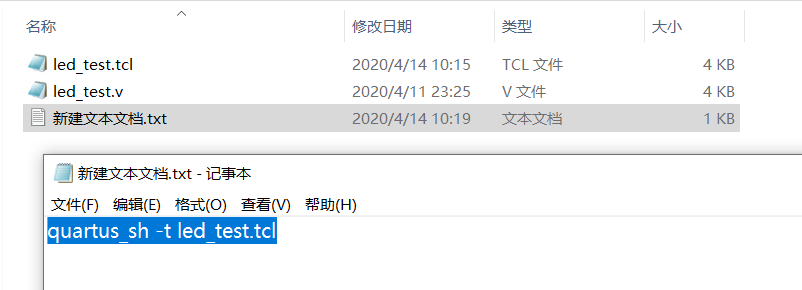

找一个已经编译好的小工程,在Quartus II中打开,点击Project -> Generate Tcl File for Project。

这时在工程目录下,会生成一个后缀为.tcl的文件。然后,大家把这个Tcl文件,与这个工程的源文件(.v)复制到一个新的文件夹下,注意文件名不要有中文字符。在文件下新建一个空白的txt文档,输入“quartus_sh -t xxx.tcl”,注意后面的tcl名需要与自己的tcl文件相同,最终的结果是这样的。

最后,将txt文档的后缀改为.bat。当双击这个.bat文件时会将原有的工程文件复制到当前目录下。这对于复制一个很大的工程时,只需要把脚本文件与源文件拷贝即可。

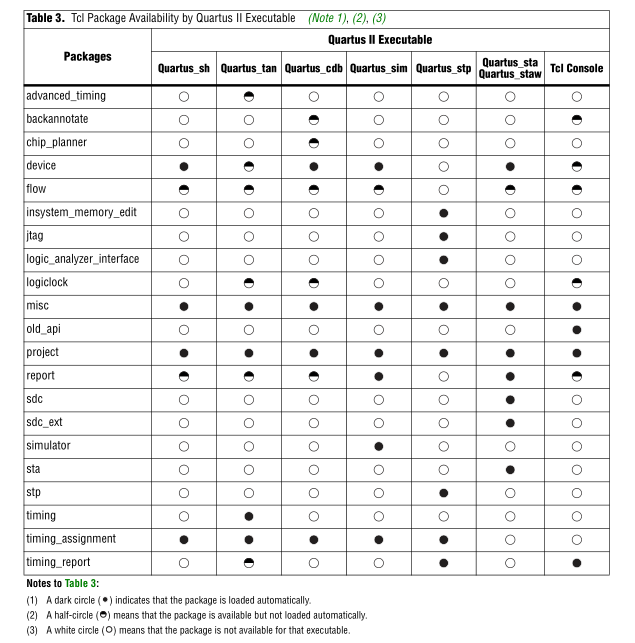

在Quartus II中,Tcl脚本有3个层次,分别是命令行可执行语句(Command-Line Executables)、Tcl内的包(Packages)与包内的命令(Package commands).

在Win+R命令行中输入quartus_sh --qhelp,可以打开Quartus II自带的关于Tcl脚本的帮助文档。

命令行可执行语句(Command-Line Executables)的形式全部为quartus_xx,是直接写入批处理脚本中的。

这里用的 quartus_sh,其实是所谓的 Quartus shell,是为所有的步骤提供了一个入口。

为了实现可执行命令所执行的功能,Quartus II里为每一个可执行命令提供了不同的包。 而包内的命令,是我们真正要往Tcl脚本里写入的。

指令与包之间的关系如下。

实心圆代表可执行语句默认加载了这个包。比如说,所有的可执行语句即quartus_xxx都加载了project这个包。这意味着,不管用任何可执行命令执行Tcl脚本,脚本中都可以调用project包下的指令,如 set_global_assignment。

空心圆代表可执行语句无法加载这个包,比如假如用quartus_sh这条语句执行sdc这个包下的语句,就是不行的。

半空半满圆代表可执行语句没有默认加载这个包,要是想用的话需要自己进行手动加载。在Tcl脚本内写入 load_package <package name>;之后,就可以使用对应包内的指令了。比如,使用quartus_sh这个指令去执行脚本,又需要执行flow这个包下的指令,如execute_flow,那么我们就需要在Tcl文件中写入 load_package flow 这句话。

总结:批处理文件(.bat)中写可执行指令,如quartus_xxx;脚本(Tcl)文件中写可执行指令下Tcl包内的指令;如果没有包没有默认导入的话还要在Tcl文件中导入。

前面示例工程生成的Tcl脚本包含两部分,第一部分为工程检测,第二部分为工程配置约束。

1 package require ::quartus::project

2

3 set need_to_close_project 0

4 set make_assignments 1

5

6 # Check that the right project is open

7 if {[is_project_open]} {

8 if {[string compare $quartus(project) "led_test"]} {

9 puts "Project led_test is not open"

10 set make_assignments 0

11 }

12 } else {

13 # Only open if not already open

14 if {[project_exists led_test]} {

15 project_open -revision led_test led_test

16 } else {

17 project_new -revision led_test led_test

18 }

19 set need_to_close_project 1

20 }

这一部分主要是检查目前待创建的工程是否存在,如果不存在的话,就project_new -revision led_test led_test,即创建led_test这个工程。其中-revision后面跟的是一同被创建的qsf文件的名字。

当然如果自己写脚本的话其实没有必要这么多判断,创建工程直接写 project_new -revision <qsf文件名> <工程名> 这样即可。

以 modelsim <安装路径>/examples/tutorials/verilog/basicSimulation 这个路径下的文件 countrer.v 和 tcounter.v 为例进行说明。

新建一个文件夹,将这两个文件放入,这里取名为modelsim_test。

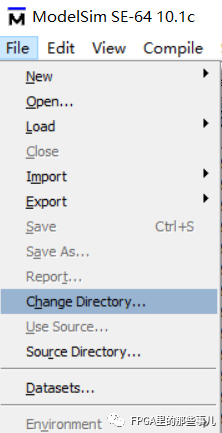

启动Modelsim,将路径切换到刚才我们新建的文件夹下。

Modelsim会把文件的编译结果放到一个虚拟的Work库中。我们要把这个虚拟的work库,与电脑硬盘上一个真正的文件夹联系起来,这个步骤就是所谓的映射。通常这个文件夹我们也会叫work,当然也可以叫其他名字。

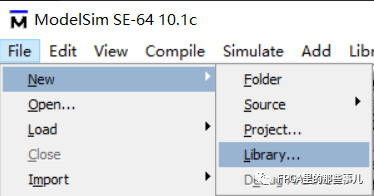

新建一个库,取名为work。

按下图操作,创建真实的work文件夹,和把文件夹与虚拟work库相连的过程。

这时Transcript的输出是:

vlib work

vmap work work

vlib work是说,在Modelsim中建立了那个真实的work文件夹。

vmap work work是说,将Modelsim中的虚拟work库关联到我们vlib的那个真实的work文件夹。

所以也可以写成:

vlib dework

vmap work dework

执行这一步后,文件夹下多了一个名为work的文件夹。同时,Modelsim中也多了一个叫做work的库。

点击Compile > Compile,将两个文件都编译到work库下。

【注】如果文件中包含IP核的话,也要将IP核的库文件复制到这个文件夹下,然后一同编译。

之后点击 compile -> done。此时,work库下面出现了这两个文件。

注意Transcript的输出,这里的vlog就是"编译"的Tcl代码。

vlog -reportprogress 300 -work work C:/Users/13613/Desktop/modelsim_test/counter.v

vlog -reportprogress 300 -work work C:/Users/13613/Desktop/modelsim_test/tcounter.v

接下来可以进行仿真了,点击Simulate > Start Simulation 将work库中的tcounter选中。将Optimization的小勾去掉(防止非预期优化,也是大多数情况下不出波形的原因)。

以下是Transcript的输出,vsim是Tcl中"仿真"的意思。

vsim -gui -novopt work.test_counter

将信号添加到波形图中。对应输出的Tcl脚本:

add wave sim:/test_counter/*

最后点击执行,对应Tcl脚本。

run

之后就出现波形了。

1. 首先建立一个test文件夹,里面放着仿真文件 XX_tb.v,然后在这test文件夹里放一个sim文件夹,在此文件夹内新建一个sim.tcl文件,这样后面的工程和乱七八糟的文件都在内部的sim文件夹里。

2. 在sim .tcl文件里写好以下代码,这些代码建议保存或制作成代码片段,以后只需要稍微改一改就能用。

1 # ==========================================================================

2 # == 清空软件残留信息

3 # ==========================================================================

4

5 # 退出之前仿真

6 quit -sim

7

8 # 清空信息

9 .main clear

10

11 # ==========================================================================

12 # == 建立工程并仿真

13 # ==========================================================================

14

15 # 建立新的工程库

16 vlib work

17

18 # 映射逻辑库到物理目录

19 vmap work work

20

21 # 编译仿真文件

22 vlog ./../*.v

23

24 # 编译设计文件

25 vlog ./../../rtl/*.v

26

27 # 无优化simulation *** 请修改文件名 ***

28 vsim -novopt work.fsm_tb

29

30 # 打开波形窗口

31 view wave

32 view structure

33

34 #打开信号窗口

35 view signals

36

37

38 # ==========================================================================

39 # == 状态机名称查看器,如若不用请删除!!!

40 # ==========================================================================

41

42 # 结构体设置

43 virtual type {

44 {4‘b0001 S0}

45 {4‘b0010 S1}

46 {4‘b0100 S2}

47 {4‘b1000 S3}

48 } fsm_type;

49

50 # 结构体和信号名关联,命名为state_name

51 virtual function {(fsm_type)/fsm_tb/u_fsm/state} state_name

52

53 # ==========================================================================

54 # == 加载波形

55 # ==========================================================================

56

57 # 添加波形,高度30,以unsigned格式显示 *** 请修改路径名 ***

58 add wave -height 30 -radix unsigned /fsm_tb/u_fsm/*

59

60 #运行

61 run 10 ms

62

63 # 跑完

64 run -all

3.之后在文件夹下再新建一个文本文件,输入

::请按任意键继续...

pause

::打开Modelsim并执行do sim.tcl

vsim -do sim.tcl

再将后缀由.txt改为.bat,使用的时候双击这个bat文件即可。

————————————————

原文链接1:Vivado Tcl使用 —— 自定义命令设计

原文链接2:手把手教你用Tcl脚本进行Modelsim仿真

原文链接3:Modelsim——工程建立和常用设置

标签:tool 命名 asi rgba 说明 物理 puts 帮助文档 mic

原文地址:https://www.cnblogs.com/yiquwange/p/14919730.html