标签:str 导致 存储 height 经济 单元 寄存器 就会 形式

前段时间“误入歧途”,直到看到了这句话:

关于底层的细节,要适度打开,很多时候保持黑箱即可,因为打开这个黑箱,你就会发现黑箱会变成黑洞,

吞噬你所有的精力和时间,有可能使你偏离原来的方向,陷入到不必要的细节中无法自拔

最近在理解一些中间件和高并发的原理知识,慢慢的又落回到了对CPU,操作系统,IO的这些底层设计的理解上

有些东西以前学习的时候没有get到关键点,现在重新看,又有些新感悟,要抓住"性能"这个点,其实就是要快,快,快

这个时候就需要了解CPU,缓存,内存的一些设计了,毕竟"经济基础决定上层建筑"

下面回顾下关键词和关键点

一、速度

在另一篇打基础的博文中,介绍了计算机存储结构层次的速度金字塔

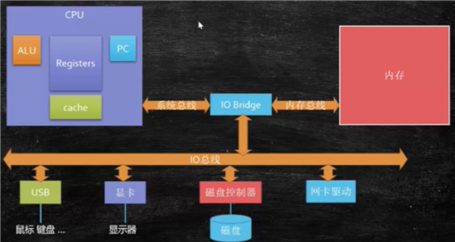

CPU-高速缓存-主存-磁盘,速度依次倍速递减,各存储由总线连接传输数据,如下图

二、CPU,高速缓存,主存之间的关系

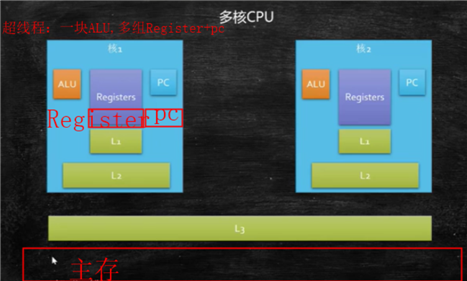

高速缓存又被分成了L1/L2/L3,L3中的缓存数据是多核CPU公用的,每个CPU又分别配置了L1+L2缓存

速度上:L1>L2>L3,因此L1是直接和寄存器相连,L3与主存相连

4核8线程,这种是4个核,每个核上的ALU配置2组 "寄存器+程序计数器",

因为CPU进行线程上下文切换时,要保存现场,切回来又要恢复现场,ALU如果对应2组Register+pc,可以大大减少切换带来的浪费

三、缓存行和局部性原理

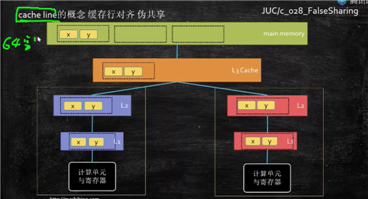

局部性原理:是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中

主存中的数据存和取都是以数据块的形式进行的,一个cacheline一般是64byte

保留知识:disruptor

四、缓存一致性协议

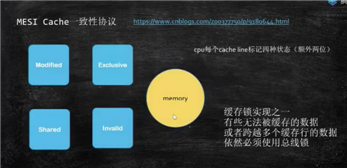

既然用到了缓存,如果是多个CPU,多个线程,那么同时加载到缓存的同一份数据被修改后就会出现不一致,可能导致错误

缓存一致性协议就是设计来解决这个问题的

标签:str 导致 存储 height 经济 单元 寄存器 就会 形式

原文地址:https://www.cnblogs.com/yb38156/p/14933950.html