标签:http ar sp strong on bs ad ef 工作

一、简介

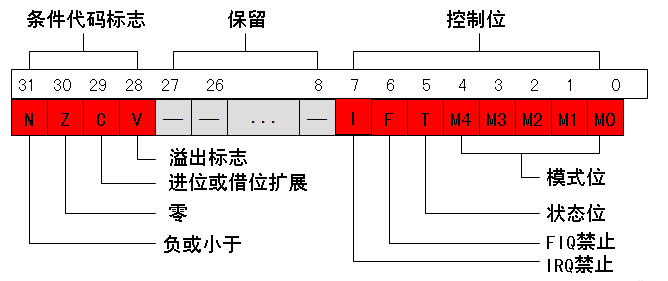

CPSR(当前程序状态寄存器)在任何处理器模式下被访问。它包含了【条件标志位】、【中断禁止位】、【当前处理器模式标志】以及其他的一些控制和状态位。每一种处理器模式下都有一个专用的物理状态寄存器,称为SPSR (备份程序状态寄存器)。

当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断退出时,可以用SPSR来恢复CPSR。由于用户模式和系统模式不是异常中断模式(因为这两种模式不会抢占其他模式,所以不需要保存状态寄存器),所以他没有SPSR。当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。

三、条件码标志

N、Z、C、V均为条件码标志位。它们的内容可被算术或逻辑运算的结果所改变,并且可以决定某条指令是否被执行。条件码标志各位的具体含义如下表所示:

| 标志位 | 含 义 |

| N | 当用两个补码表示的有符号数进行运算时,N=1表示运算的结果为负数;N=0表示运算的结果为正数或零 |

| Z | Z=1表示运算的结果为零,Z=0表示运算的结果非零。 |

| C | -加法运算(包括CMP):当运算结果产生了进位时(无符号数溢出),C=1,否则C=0。 -减法运算(包括CMP):当运算时产生了借位时(无符号数溢出),C=0,否则C=1。 -对于包含移位操作的非加/减运算指令,C为移出值的最后一位。 -对于其它的非加/减运算指令,C的值通常不会改变。 |

| V | -对于加减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出 -对于其它的非加/减运算指令,V的值通常不会改变。 |

四、控制位

CPSR的低八位I、F、T、M[4:0]统称为控制位。当异常中断发生时这些位发生变化。在特权级的处理器模式下,软件可以修改这些控制位。

I: IRQ中断禁止位:当I=1时禁止IRQ中断,

F: FIQ中断禁止位:当F=1时禁止FIQ中断

T: T控制位该位反映处理器的运行状态。当该位为1时,程序运行于THUMB状态,否则运行于ARM状态。该信号反映在外部引脚TBIT上。在程序中不得修改CPSR中的TBIT位,否则处理器工作状态不能确定。

运行模式位M[4:0]:这几位是模式位,这些位决定了处理器的运行模式。具体含义如下表所示:

| M[4:0] | 处理器模式 | ARM模式可访问的寄存器 | THUMB模式可访问的寄存器 |

| 0b10000 | 用户模式 | PC,CPSR,R0~R14 | PC,CPSR,R0~R7,LR,SP |

| 0b10001 | FIQ模式 | PC,CPSR,SPSR_fiq,R14_fiq~R8_fiq,R0~R7 | PC,CPSR,SPSR_fiq,LR_fiq,SP_fiq,R0~R7 |

| 0b10010 | IRQ模式 | PC,CPSR,SPSR_irq,R14_irq~R13_irq,R0~R12 | PC,CPSR,SPSR_irq,LR_irq,SP_irq,R0~R7 |

| 0b10011 | 管理模式 | PC,CPSR,SPSR_svc,R14_svc~R13_svc,R0~R12 | PC,CPSR,SPSR_svc,LR_svc,SP_svc,R0~R7 |

| 0b10111 | 中止模式 | PC,CPSR,SPSR_abt,R14_abt~R13_abt,R0~R12 | PC,CPSR,SPSR_abt,LR_abt,SP_abt,R0~R7 |

| 0b11011 | 未定义模式 | PC,CPSR,SPSR_und,R14_und~R13_und,R0~R12 | PC,CPSR,SPSR_und,LR_und,SP_und,R0~R7 |

| 0b11111 | 系统模式 | PC,CPSR,R0~R14 | PC,CPSR,LR,SP,R0~R74 |

标签:http ar sp strong on bs ad ef 工作

原文地址:http://www.cnblogs.com/famer/p/4117091.html