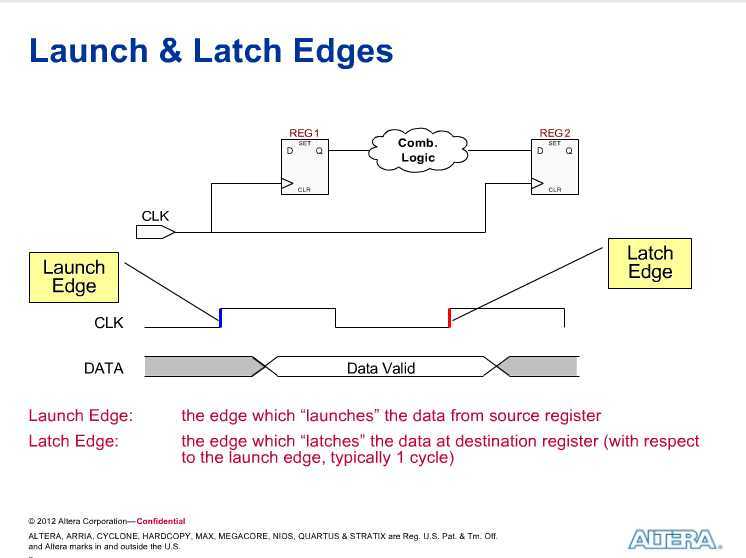

1、如果启动沿(launch)和锁存沿(latch)是同一时钟域则,latch比launch晚一个时钟周期。

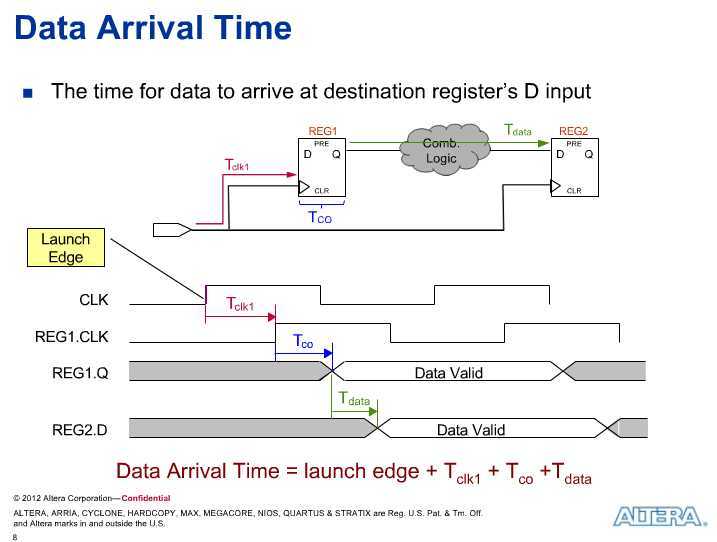

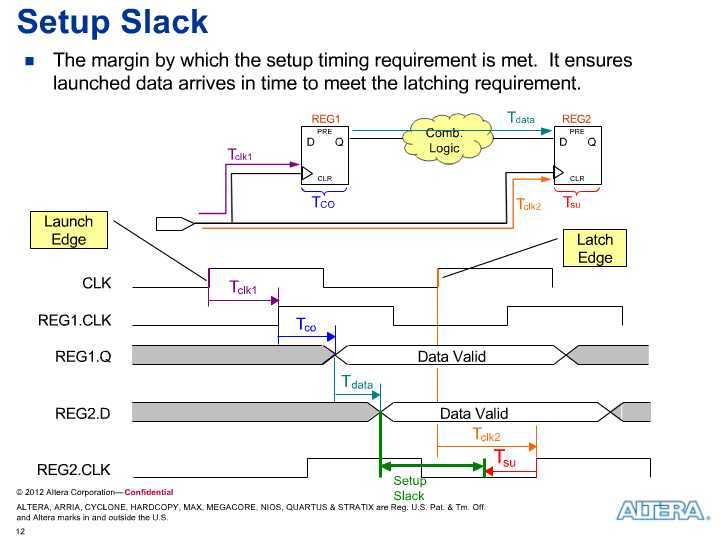

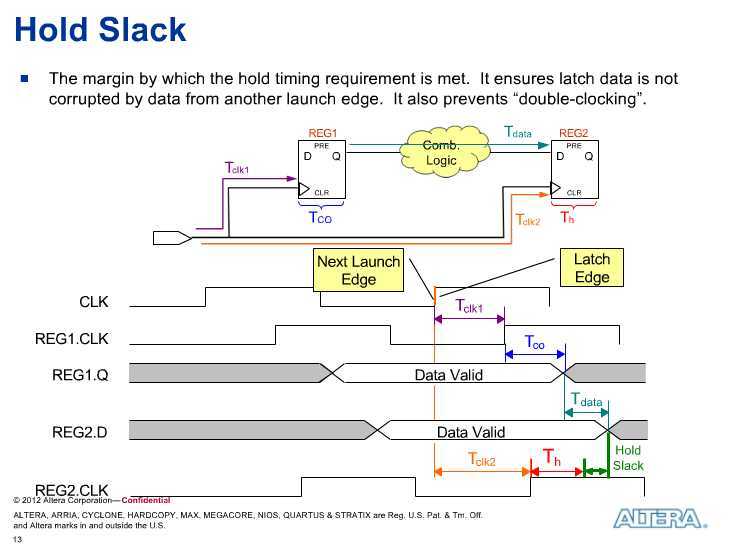

2、数据到达时间

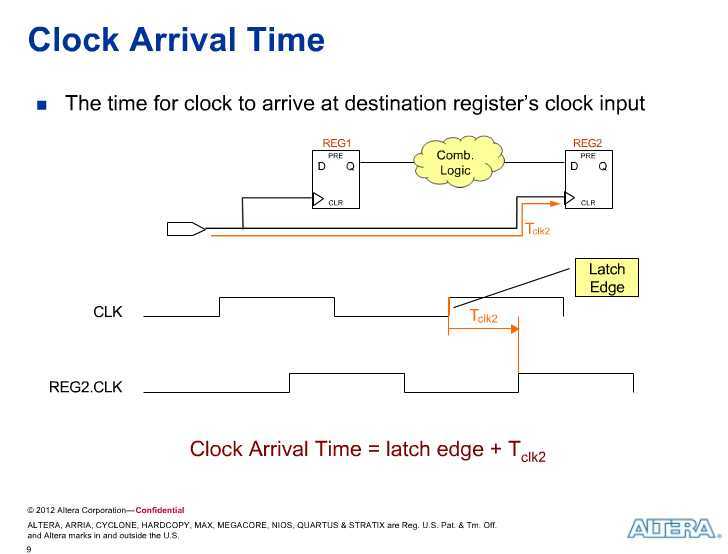

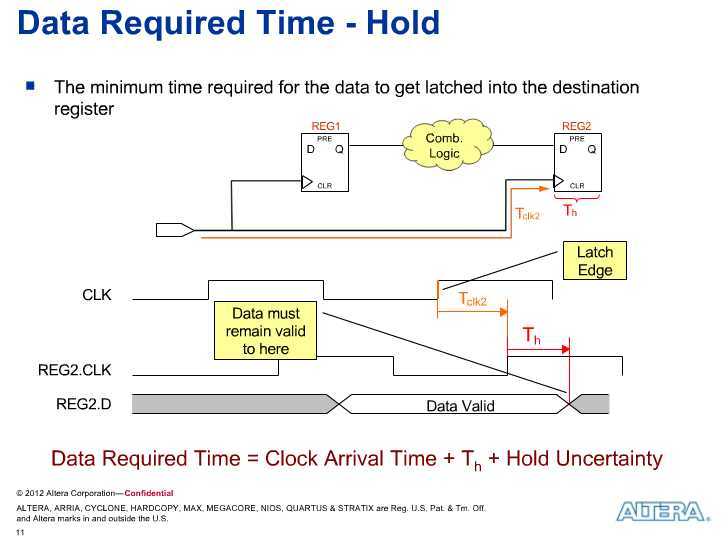

3、时钟到达时间。如果启动沿(launch edge)和锁存沿(latch edge)是同一时钟域则,latch edge比launch edge晚一个时钟周期。如果在不同的时钟域,launch edge和latch edge的时间差就根据具体的时间。

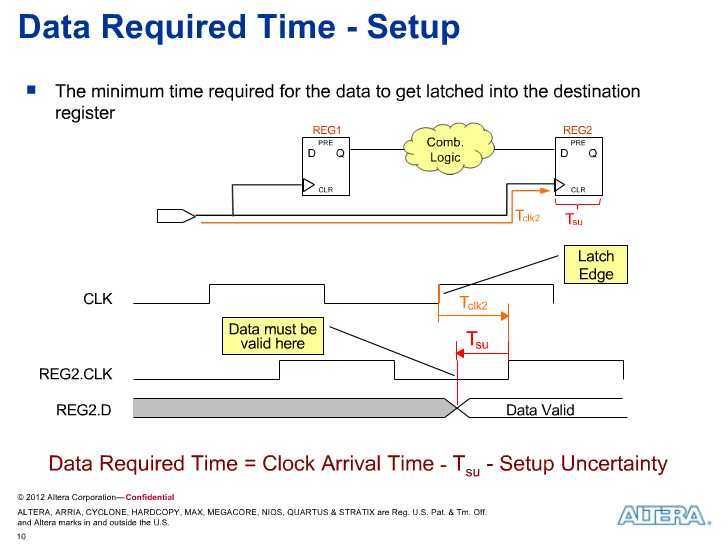

4、数据到达时间,建立时间

5、数据到达时间,保持时间

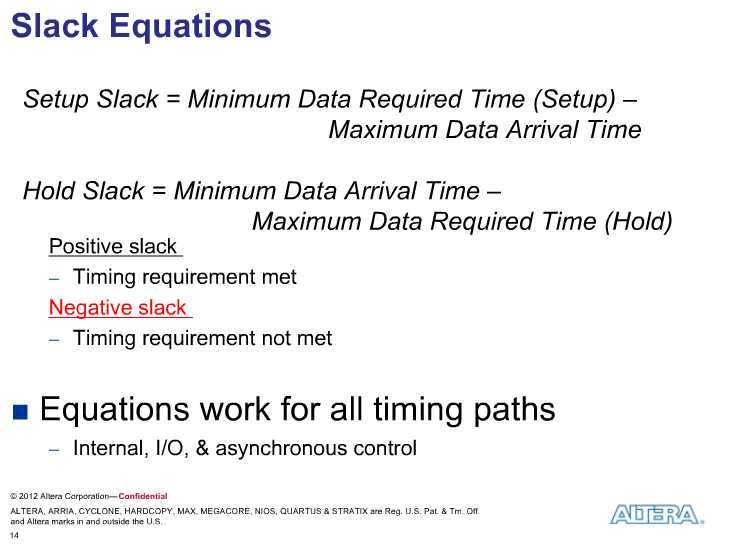

6、建立时间余量

7、保持时间余量

8、总结的时间余量公式

第二部分

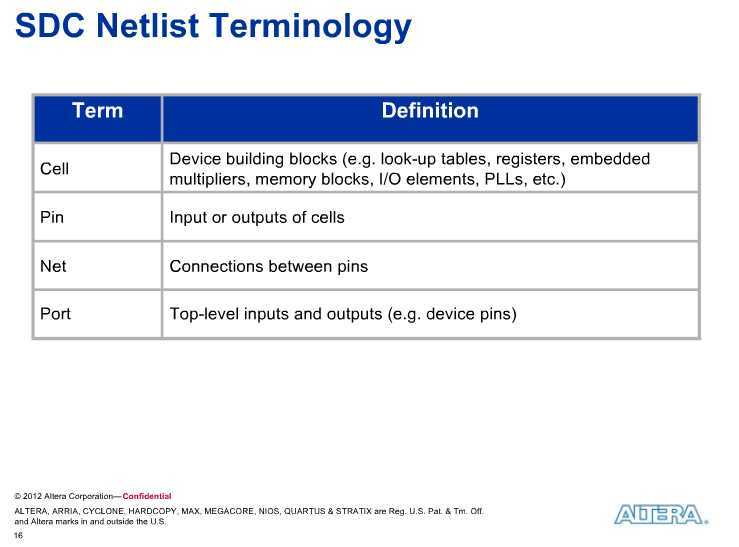

9、单元(cell),引脚(pin),网(net),端口(port)的定义

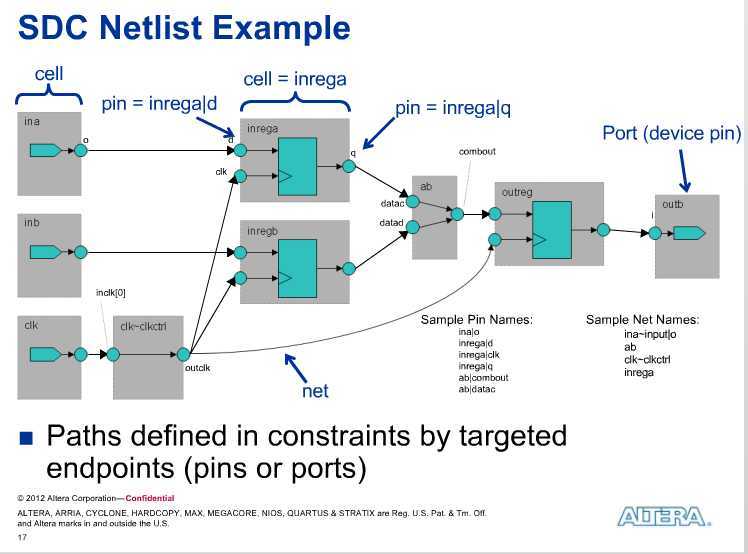

10、具体的实例

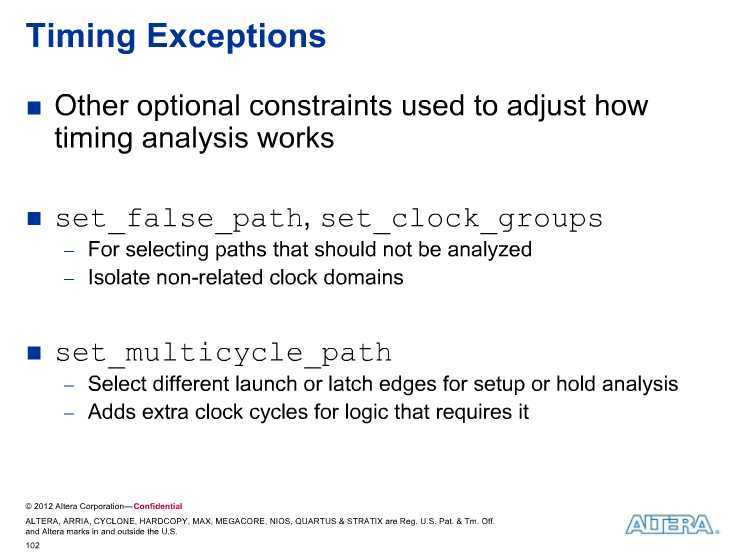

11、约束顺序:

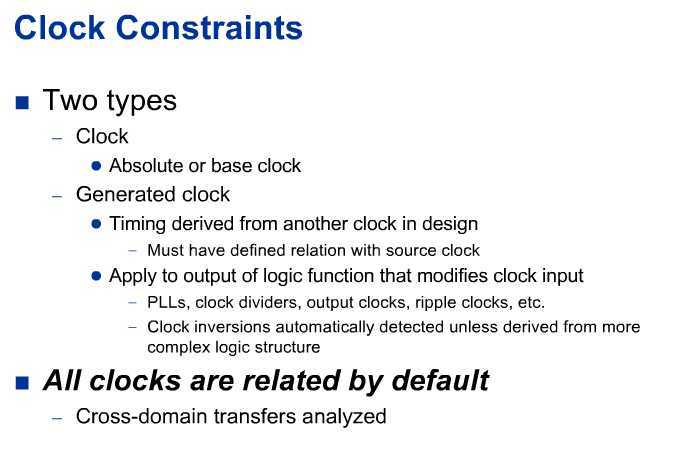

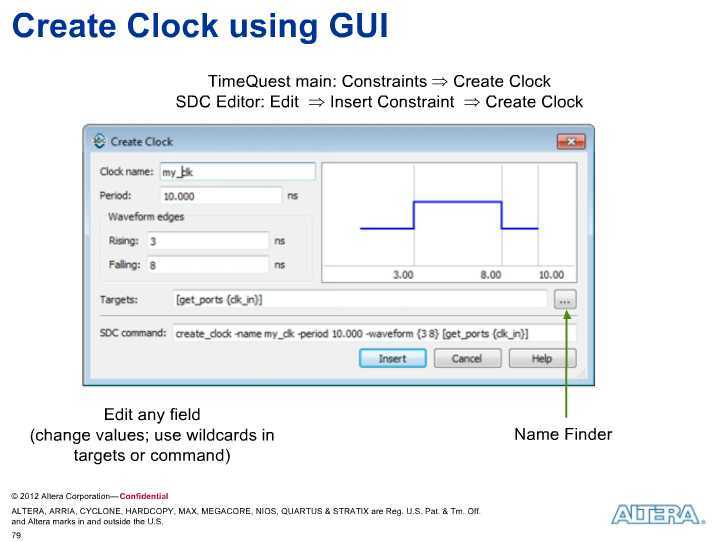

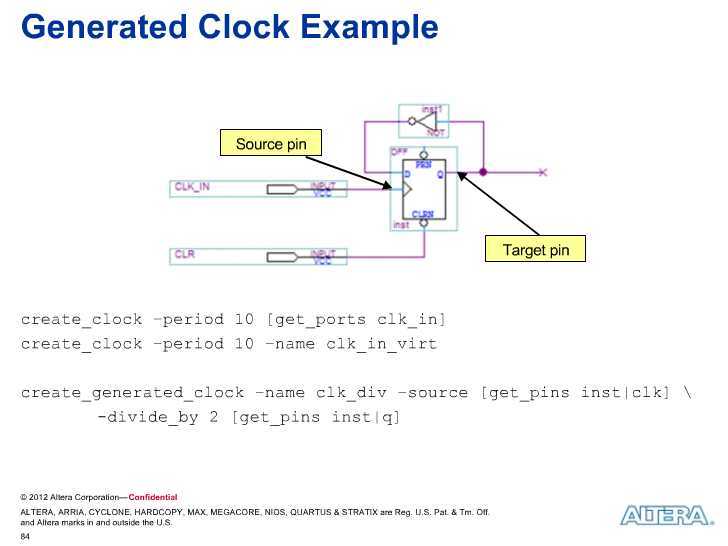

1)creat clock,产生时钟。

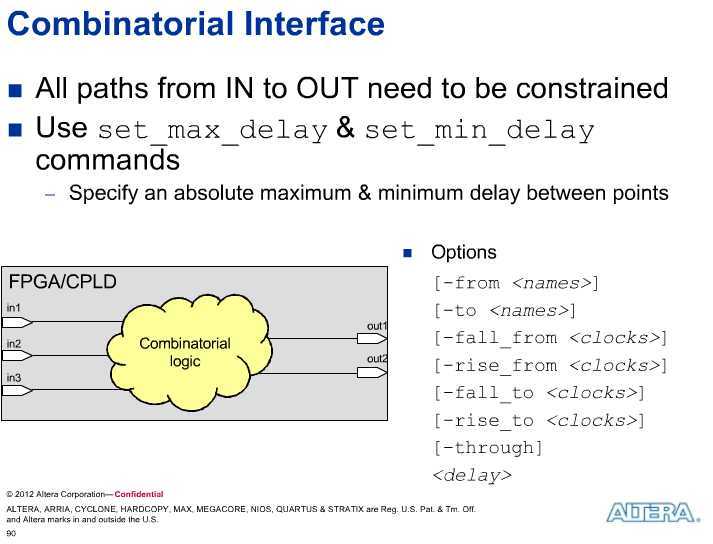

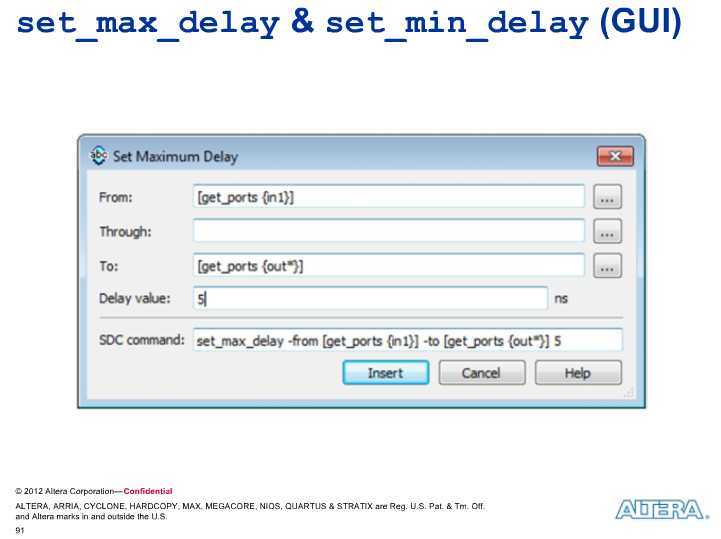

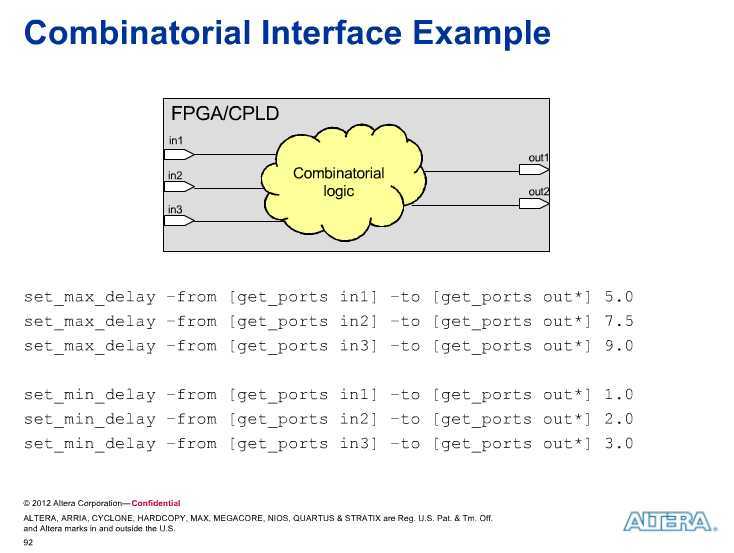

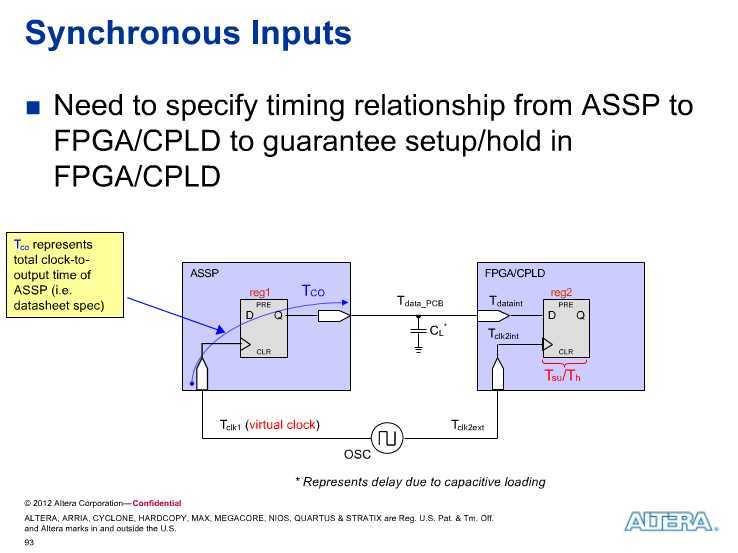

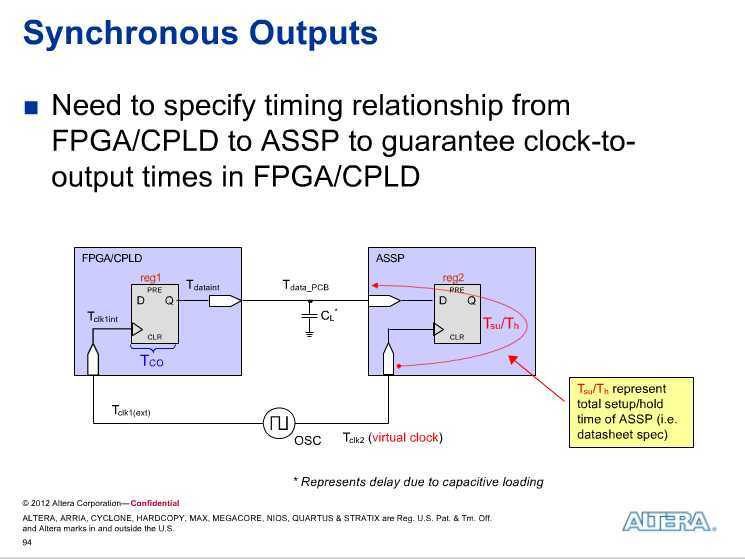

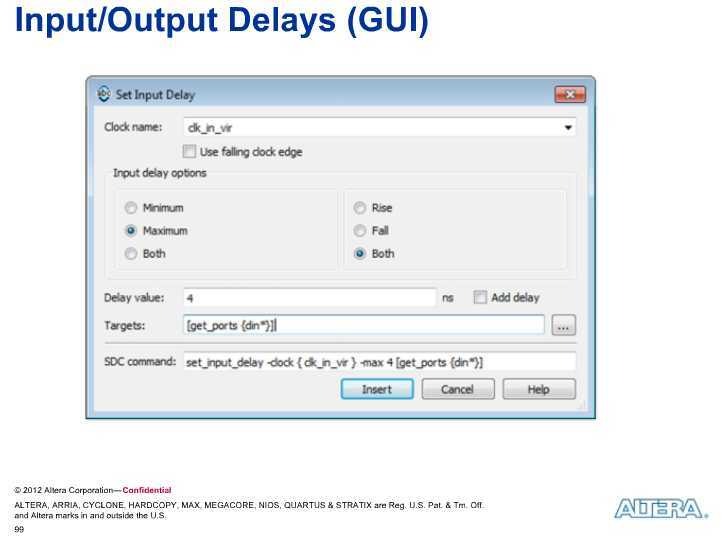

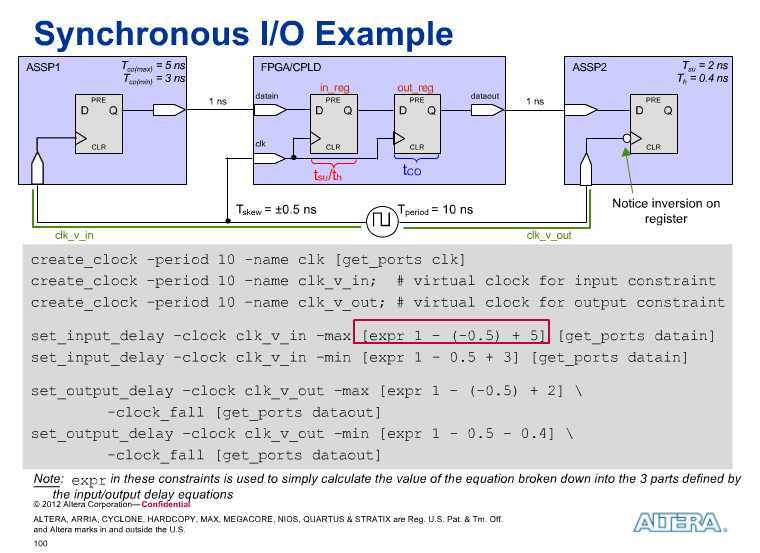

2)IO端口的结束:如果输入输出只通过组合逻辑,则可以使用set_max_delay & set_min_delay进行约束。如果是同步输入和输出可以建立虚拟时钟进行约束。

-* :表示这个输入到任何输出。

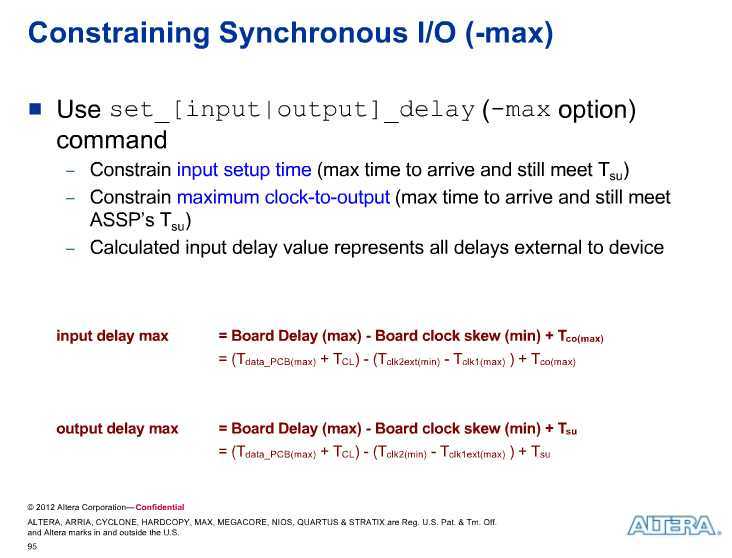

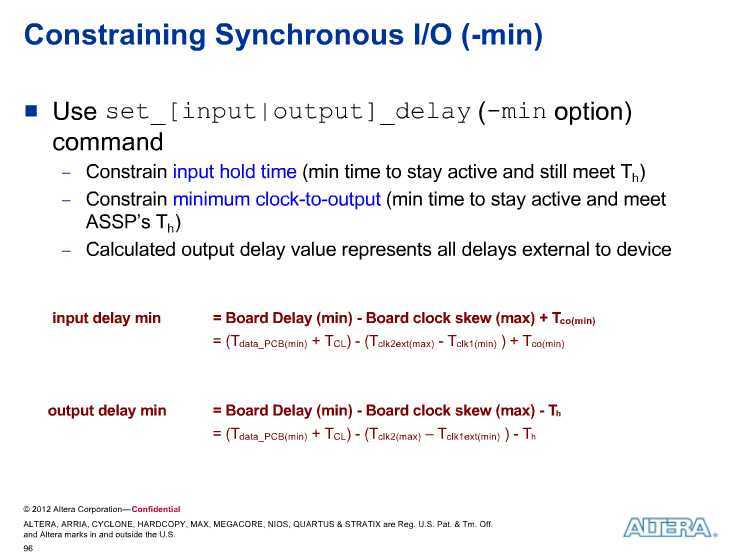

虚拟时钟的max, min

学习 altera官网 之 timequest,布布扣,bubuko.com

原文地址:http://www.cnblogs.com/cornhill/p/3737722.html