标签:style blog http ar color os 使用 sp on

SOS信号:. . . _ _ _ . . .

1.

module sos_module ( CLK, RSTn, Pin_Out, SOS_En_Sig ); input CLK; input RSTn; input SOS_En_Sig; output Pin_Out; /****************************************/ parameter T1MS = 16‘d49_999;//DB4CE15开发板使用的晶振为50MHz,50M*0.001-1=49_999 /***************************************/ reg [15:0]Count1; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count1 <= 16‘d0; else if( isCount && Count1 == T1MS ) Count1 <= 16‘d0; else if( isCount ) Count1 <= Count1 + 1‘b1; else if( !isCount ) Count1 <= 16‘d0; /****************************************/ reg [9:0]Count_MS; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count_MS <= 10‘d0; else if( isCount && Count1 == T1MS ) Count_MS <= Count_MS + 1‘b1; else if( !isCount ) Count_MS <= 10‘d0; /******************************************/ reg isCount; reg rPin_Out; reg [4:0]i; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin isCount <= 1‘b0; rPin_Out <= 1‘b0; i <= 5‘d0; end else case( i ) 5‘d0 : if( SOS_En_Sig ) i <= 5‘d1; 5‘d1, 5‘d3, 5‘d5, 5‘d13, 5‘d15, 5‘d17 : if( Count_MS == 10‘d100 ) begin isCount <= 1‘b0; rPin_Out <= 1‘b0; i <= i + 1‘b1; end // short else begin isCount <= 1‘b1; rPin_Out <= 1‘b1; end 5‘d7, 5‘d9, 5‘d11 : if( Count_MS == 10‘d300 ) begin isCount <= 1‘b0; rPin_Out <= 1‘b0; i <= i + 1‘b1; end // long else begin isCount <= 1‘b1; rPin_Out <= 1‘b1; end 5‘d2, 5‘d4, 5‘d6, 5‘d8, 5‘d10, 5‘d12, 5‘d14, 5‘d16, 5‘d18 : if( Count_MS == 10‘d50 ) begin isCount <= 1‘b0; i <= i + 1‘b1; end// interval else isCount <= 1‘b1; 5‘d19 : begin rPin_Out <= 1‘b0; i <= 5‘d0; end // end endcase /***************************************************/ assign Pin_Out = rPin_Out; /***************************************************/ endmodule

2.

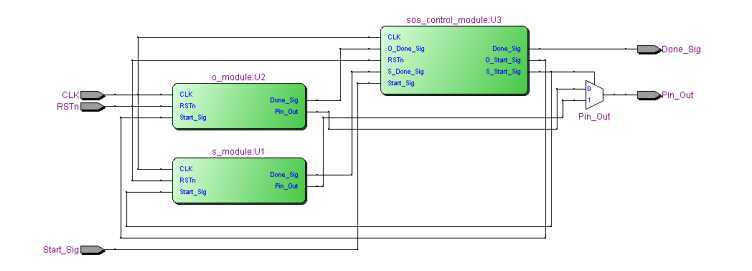

“Start_Sig”如同 C 语言中的调用指令,“Done_Sig”如同 C 语言的返回指令。这两个信号的存在就是为了控制模块的调用。

module sos_control_module ( CLK, RSTn, Start_Sig, S_Done_Sig, O_Done_Sig, S_Start_Sig, O_Start_Sig, Done_Sig ); input CLK; input RSTn; input Start_Sig; input S_Done_Sig, O_Done_Sig; output S_Start_Sig, O_Start_Sig; output Done_Sig; /*************************************/ reg [3:0]i; reg isO; reg isS; reg isDone; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin i <= 4‘d0; isO <= 1‘b0; isS <= 1‘b0; isDone <= 1‘b0; end else if( Start_Sig ) case( i ) 4‘d0: if( S_Done_Sig ) begin isS <= 1‘b0; i <= i + 1‘b1; end else isS <= 1‘b1; 4‘d1: if( O_Done_Sig ) begin isO <= 1‘b0; i <= i + 1‘b1; end else isO <= 1‘b1; 4‘d2: if( S_Done_Sig ) begin isS <= 1‘b0; i <= i + 1‘b1; end else isS <= 1‘b1; 4‘d3: begin isDone <= 1‘b1; i <= 4‘d4; end 4‘d4: begin isDone <= 1‘b0; i <= 4‘d0; end endcase /*****************************************/ assign S_Start_Sig = isS; assign O_Start_Sig = isO; assign Done_Sig = isDone; /*****************************************/ endmodule

module s_module ( CLK, RSTn, Start_Sig, Done_Sig, Pin_Out ); input CLK; input RSTn; input Start_Sig; output Done_Sig; output Pin_Out; /****************************************/ parameter T1MS = 16‘d49_999; /***************************************/ reg [15:0]Count1; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count1 <= 16‘d0; else if( Count1 == T1MS ) Count1 <= 16‘d0; else if( isCount ) Count1 <= Count1 + 1‘b1; else if( !isCount ) Count1 <= 16‘d0; /****************************************/ reg [9:0]Count_MS; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count_MS <= 10‘d0; else if( Count_MS == rTimes ) Count_MS <= 10‘d0; else if( Count1 == T1MS ) Count_MS <= Count_MS + 1‘b1; /******************************************/ reg [3:0]i; reg rPin_Out; reg [9:0]rTimes; reg isCount; reg isDone; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin i <= 4‘d0; rPin_Out <= 1‘b0; rTimes <= 10‘d1000; isCount <= 1‘b0; isDone <= 1‘b0; end else if( Start_Sig ) case( i ) 4‘d0, 4‘d2, 4‘d4: if( Count_MS == rTimes ) begin rPin_Out <= 1‘b0; isCount <= 1‘b0; i <= i + 1‘b1; end else begin isCount <= 1‘b1; rPin_Out <= 1‘b1; rTimes <= 10‘d100; end 4‘d1, 4‘d3, 4‘d5: if( Count_MS == rTimes ) begin isCount <= 1‘b0; i <= i + 1‘b1; end else begin isCount <= 1‘b1; rTimes <= 10‘d50; end 4‘d6: begin isDone <= 1‘b1; i <= 4‘d7; end 4‘d7: begin isDone <= 1‘b0; i <= 4‘d0; end endcase /******************************************/ assign Done_Sig = isDone; assign Pin_Out = !rPin_Out; /******************************************/ endmodule

module o_module ( CLK, RSTn, Start_Sig, Done_Sig, Pin_Out ); input CLK; input RSTn; input Start_Sig; output Done_Sig; output Pin_Out; /****************************************/ parameter T1MS = 17‘d49_999; /***************************************/ reg [16:0]Count1; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count1 <= 17‘d0; else if( Count1 == T1MS ) Count1 <= 17‘d0; else if( isCount ) Count1 <= Count1 + 1‘b1; else if( !isCount ) Count1 <= 17‘d0; /****************************************/ reg [9:0]Count_MS; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) Count_MS <= 10‘d0; else if( Count_MS == rTimes ) Count_MS <= 10‘d0; else if( Count1 == T1MS ) Count_MS <= Count_MS + 1‘b1; /******************************************/ reg [3:0]i; reg rPin_Out; reg [9:0]rTimes; reg isCount; reg isDone; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin i <= 4‘d0; rPin_Out <= 1‘b0; rTimes <= 10‘d1000; isCount <= 1‘b0; isDone <= 1‘b0; end else if( Start_Sig ) case( i ) 4‘d0, 4‘d2, 4‘d4: if( Count_MS == rTimes ) begin rPin_Out <= 1‘b0; isCount <= 1‘b0; i <= i + 1‘b1; end else begin isCount <= 1‘b1; rPin_Out <= 1‘b1; rTimes <= 10‘d400; end 4‘d1, 4‘d3, 4‘d5: if( Count_MS == rTimes ) begin isCount <= 1‘b0; i <= i + 1‘b1; end else begin isCount <= 1‘b1; rTimes <= 10‘d50; end 4‘d6: begin isDone <= 1‘b1; i <= 4‘d7; end 4‘d7: begin isDone <= 1‘b0; i <= 4‘d0; end endcase /******************************************/ assign Done_Sig = isDone; assign Pin_Out = !rPin_Out; /******************************************/ endmodule

module sos_module ( CLK, RSTn, Start_Sig, Done_Sig, Pin_Out ); input CLK; input RSTn; input Start_Sig; output Done_Sig; output Pin_Out; /*****************************/ wire S_Done_Sig; wire S_Pin_Out; s_module U1 ( .CLK( CLK ), .RSTn( RSTn ), .Start_Sig( S_Start_Sig ), // input - from U3 .Done_Sig( S_Done_Sig ), // output - to U3 .Pin_Out( S_Pin_Out ) // output - to selector ) ; /*********************************/ wire O_Done_Sig; wire O_Pin_Out; o_module U2 ( .CLK( CLK ), .RSTn( RSTn ), .Start_Sig( O_Start_Sig ), // input - from U3 .Done_Sig( O_Done_Sig ), // output - to U3 .Pin_Out( O_Pin_Out ) // output - to selector ); /*********************************/ wire S_Start_Sig; wire O_Start_Sig; sos_control_module U3 ( .CLK( CLK ), .RSTn( RSTn ), .Start_Sig( Start_Sig ), // input - from top .S_Done_Sig( S_Done_Sig ), // input - from U1 .O_Done_Sig( O_Done_Sig ), // input - from U2 .S_Start_Sig( S_Start_Sig ), // output - to U1 .O_Start_Sig( O_Start_Sig ), // output - to U2 .Done_Sig( Done_Sig ) // output - to top ); /*********************************/ //selector reg Pin_Out; always @ ( * ) if( S_Start_Sig ) Pin_Out = S_Pin_Out; // select from U1 else if( O_Start_Sig ) Pin_Out = O_Pin_Out; // select from U2 else Pin_Out = 1‘bx; /*********************************/ endmodule

标签:style blog http ar color os 使用 sp on

原文地址:http://www.cnblogs.com/shaogang/p/4123489.html