标签:des blog http io ar 使用 sp on 数据

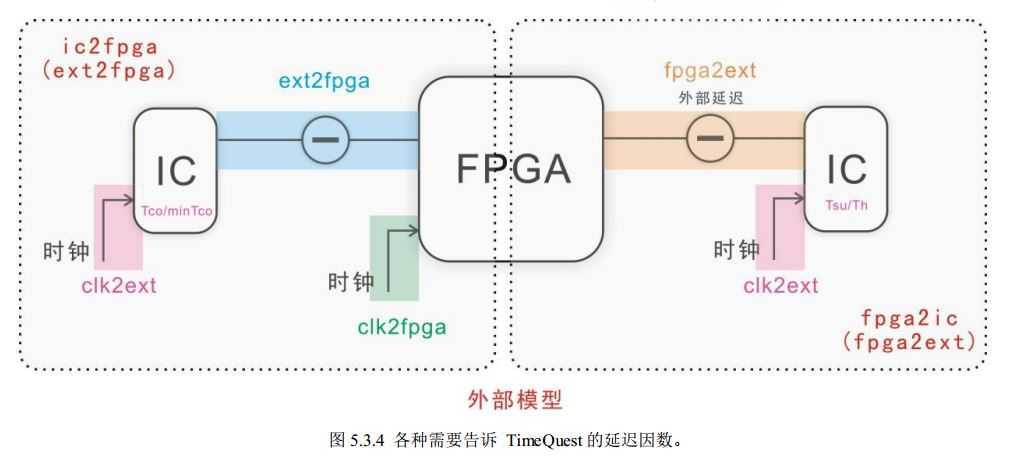

现在知道时序约束主要是FPGA to ic,或者ic to FPGA。

上图可以表示FPGA to IC, IC to FPGA.

fpga2ic:

fpga2ext 是 fpga 致 ic 信号的走线延迟;

clk2fpga 是时钟信号致 fpga 的走线延迟;

clk2ext 是时钟信号致 fpga 的走线延迟;

Tsu/Th 外部器件的寄存器特性;

( Tsu 信号建立时间; Th 信号保持时间)

ic2fpga:

ext2fpga 是 ic 致 fpga 信号的走线延迟;

clk2fpga 是时钟信号致 fpga 的走线延迟;

clk2ext 是时钟信号致 fpga 的走线延迟;

Tco/minTco 外部器件的寄存器特性;

( Tco 信号输出时间; minTco 最小信号输出时间)

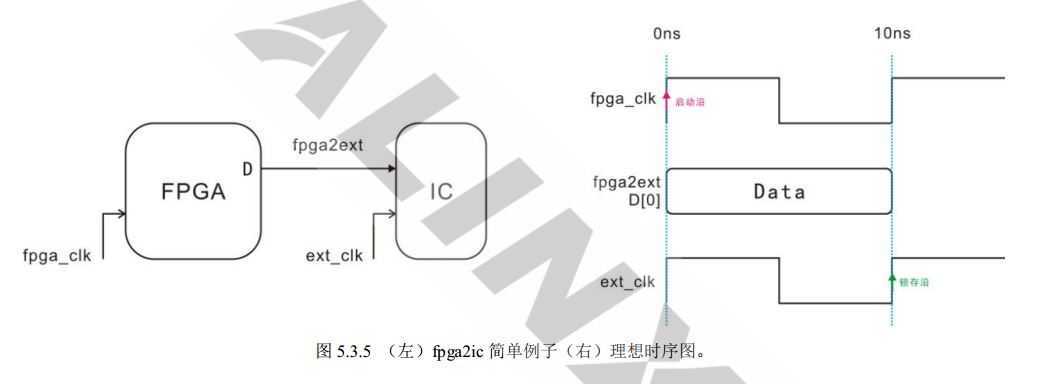

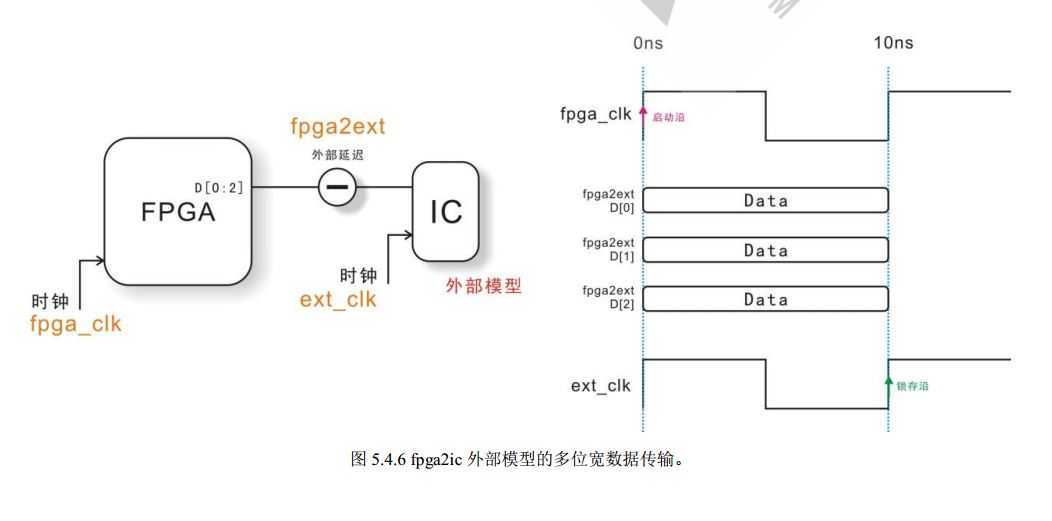

先来看看FPGA2IC:

上图是FPGA to ic 的信号连接。我写的sram,uart 和这个 还是有点区别因为只有数据线,没有clk。

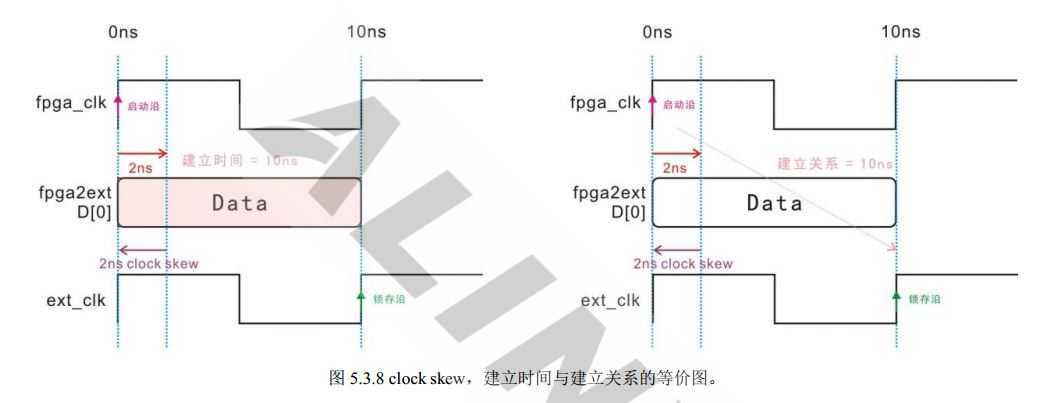

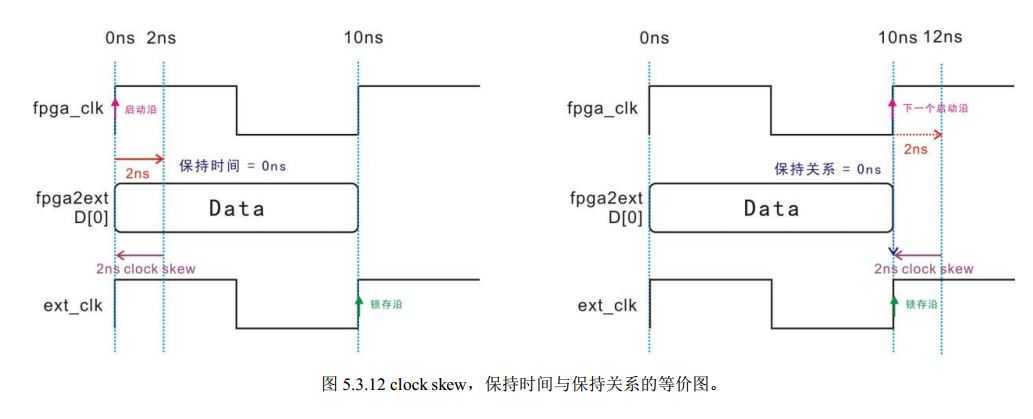

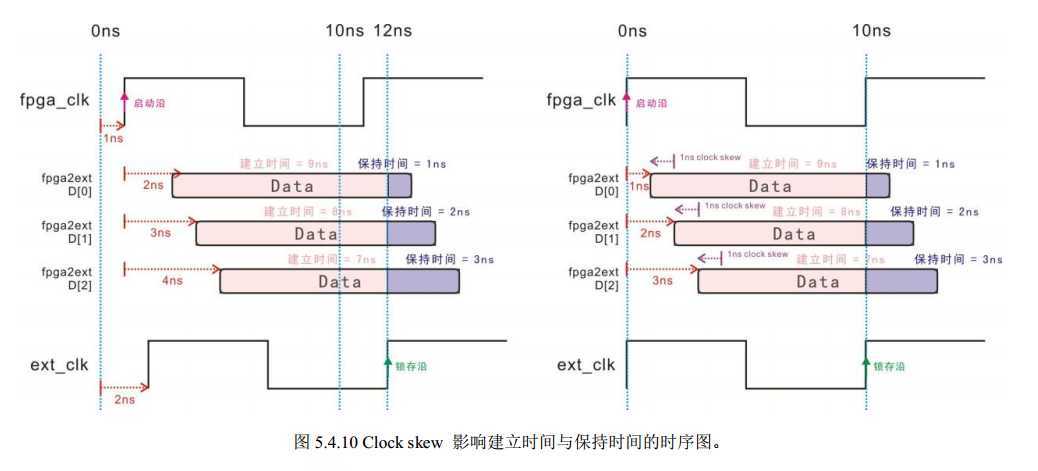

clock skew 结果最终会直接作用在数据的延迟上。这是非常重要的一点。clock skew = < destination reg clock delay > - < source reg clock delay >

对 fpga2ic 的外模型而言, fpga_clk 是源寄存器时钟然而 ext_clk 是目的寄存器时钟。

data delay = 2ns

data delay‘ = <data delay> - <clock skew>

= 2ns - 2ns

= 0ns

data delay 数据延迟

data delay‘ 时钟差作用后的数据延迟

上图表示:数据延迟2ns,即2ns数据才到达目的寄存器,即建立时间8ns,但是因为时钟偏移2ns作用到数据偏移后,相当于数据没有延迟。即建立时间10ns。

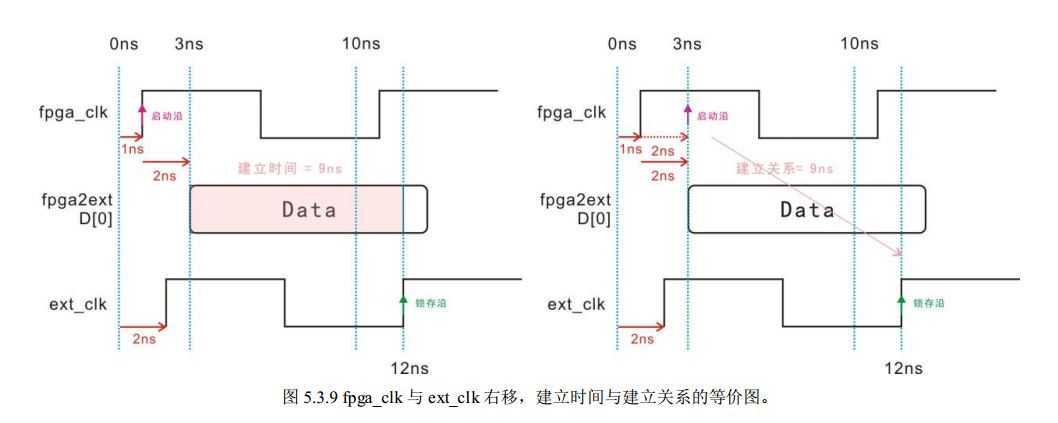

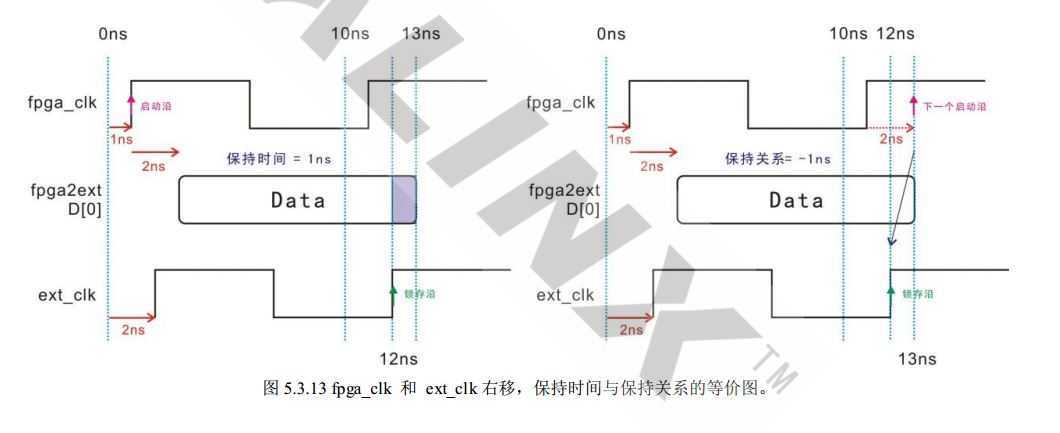

时钟偏移: 2 - 1 = 1ns, 数据延迟: 2ns, 当时钟偏移作用于数据延迟后的数据延迟次:data_delay - clock_skew = 2 - 1 = 1 ns。

以上是建立关系,下面分析保持关系:

如果使用“屁股”计算保持时间:data_arrival_time - data_aquaire_time = 2 -2 =0ns.

同理如果使用“屁股”计算: (1+2) - 2 = 1 ns。

如果将clock_skew作用于data_delay:data_delay - clock_skew = 3 - 2 = 1ns。

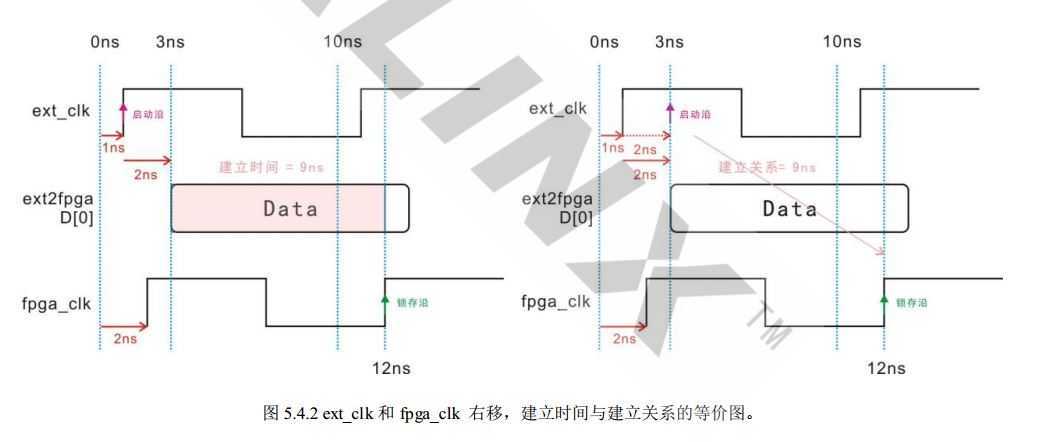

以上是FPGA to ic,接下来讨论ic to FPGA:时钟偏移作用于数据后建立时间和保持时间。

可以看出此时FPGA是接收数据,但是时钟偏移作用于数据延迟原理一样的。

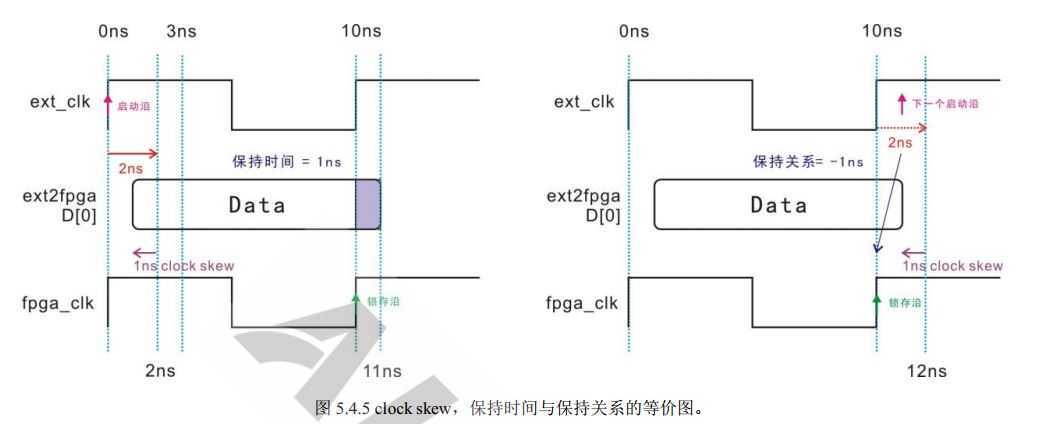

这是保持时间图。clock_delay = 1ns;data_delay = 2ns;data_delay‘ = data_delay - clock_skew = 2 - 1 = 1ns。

以上讨论的是一位位宽的,那多位位宽的呢?

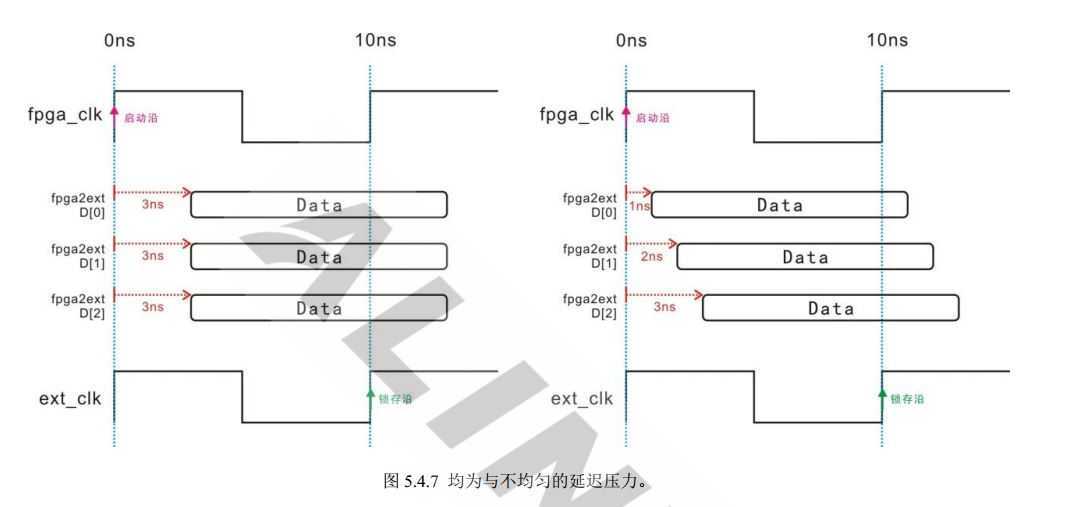

均匀与不均匀的延迟压力。

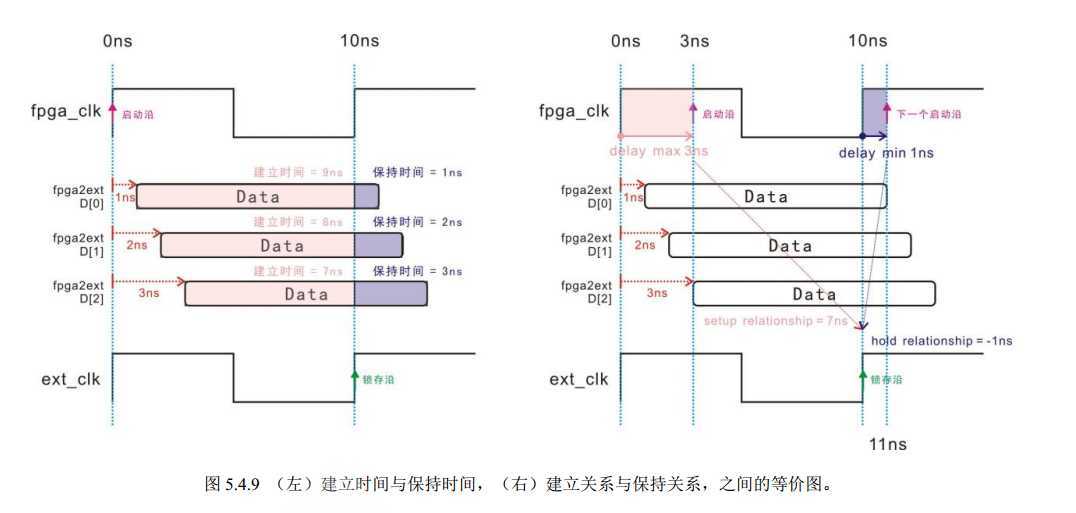

这样对保持时间和建立时间是有影响的。从上图可以看出 max_delay = 3ns, min_delay = 1ns。建立时间最危险的是D[2] = 7ns,,保持时间最危险的是D[0] = 1ns,可以知道max_delay影响建立时间,min_delay影响保持时间。如下图:

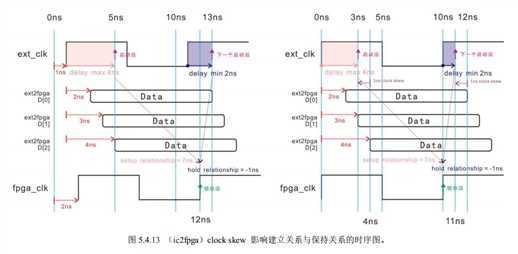

clock_skew作用于不均匀的延迟会是什么样的结果?原理还是一样的,就是将时钟偏移作用于数据而时钟保持不变。如下图:

标签:des blog http io ar 使用 sp on 数据

原文地址:http://www.cnblogs.com/cornhill/p/4023089.html