标签:

时钟概念:

★时钟脉冲:一个按一定电压幅度,一定时间间隔连续发出的脉冲信号;

★时钟频率:在单位时间(如:1秒)内产生的时钟秒冲数;

作用:

时钟信号是时序逻辑的基础

时钟的产生-晶振

晶振:晶体振荡器,是用石英晶体精密切割做成。

时钟产生-PLL

PLL:(锁相环)合成器=外部晶体+PLL电路。

S3C2440的主时钟晶振来自外部晶振(XTIPLL),或者是外部时钟(EXTCLK)。时钟生成器包含了一个振荡器(振荡放大器),其连接外部晶振,可以产生需要的高频,通过引脚OM[3:2]来决定时钟源时Crystal还是EXTCLK.

S3C2440有两个PLL:(1)MPLL和(2)UPLL,

UPLL专用于USB设备。

MPLL 用于CPU及其他外围器件。

通过MPLL会产生三个部分的时钟频率:

FCLK:用于CPU核;

HCLK:用于AHB(常用于高速外设)总线的设备,比如:SDRAM;

PCLK:用于APB(常用于低速外设)总线的设备,比如:UART.

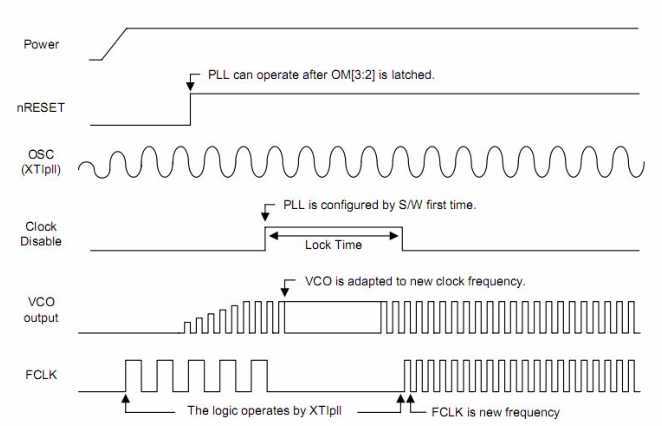

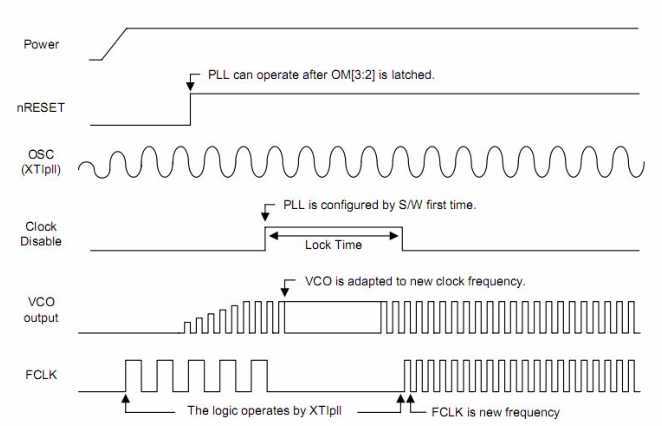

时钟启动流程:

1.上电几毫秒后,外部晶振输出稳定,FCLK=外部晶振频率(12MHZ),nRESET

信号恢复高电平后,CPU开始执行命令。

2.在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。

Lock Time的长短由寄存器LOCKTIME设定。

3.Lock Time之后,MPLL输出正常,CPU工作在新的FCLK(如:400MHZ)下。

设置S3C2440的时钟频率就是设置相关的几个寄存器:

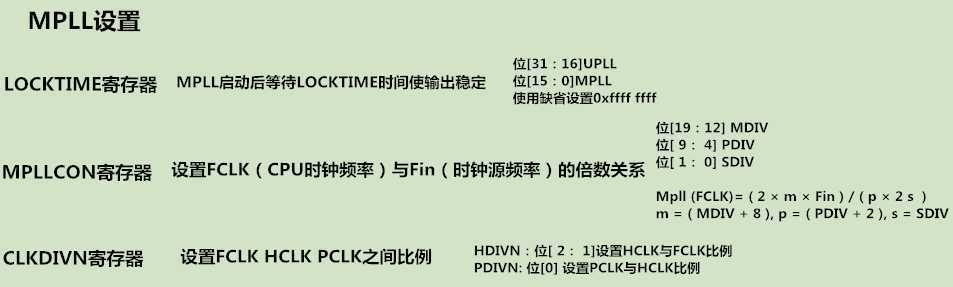

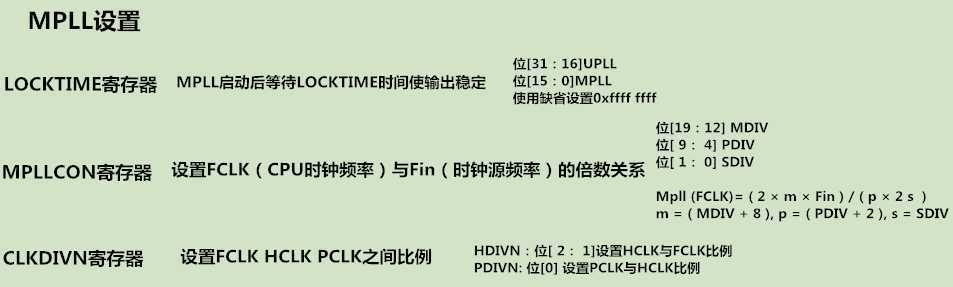

寄存器-LOCKTIME

MPLL启动后需要等待一段时间(Lock Time),使得其输出稳定。

位[31:16]用于UPLL,

位[15:0]用于MPLL.

使用缺省值0xffff ffff

寄存器-MPLLCON

该寄存器用于设置FCLK(cpu的时钟频率)与Fin的倍数(Fin:输入的时钟频率)

位[19:12]的值称为MDIV

位[9:4]的值称为PDIV

位[1:0]的值称为SDIV

FCLK与Fin的计算关系式如下:

MPLL(FCLK) = (2*m*Fin)/(p*2^s)

其中:m= MDIV+8 ,p=PDIV+2 , s= SDIV

CLKDIVN

寄存器用于设置FCLK、HCLK、PCLK三者的比例

★ HDIVN:位[2:1],用来设置HCLK与FCLK比例关系

★ PDIVN:位[0],用来设置PCLK与HCLK比例关系

例如:

FCLK:HCLK:PCLK=4:2:1

FCLK=400MHZ(主频)

HCLK=200M

PCLK=100M

时钟体系

标签:

原文地址:http://www.cnblogs.com/liuchengchuxiao/p/4179080.html