标签:

标注说明:

1、时间节点紫色字体;

2、进度情况(完成——红色字体,未完成——橙色字体);

3、文档名绿色字体

4、工程中各模块名蓝色字体

文档命名说明:

工程内容_F章节 细分小节

如HD2AV_F3B.doc,表示HD2AV工程的第三章第B小节的工程文档。

本工程共包含子文档18个。

基于FPGA的HD视频到AV视频的分辨率变换

计划表

一、视频信号处理基础理论知识

1、内容

了解高清1080p高清信号的视频图像格式以及需要转换的AV视频信号的图像格式。

2、进度计划

(1)时间节点:2014/12/12~2014/12/13

(2)进展进度:已完成

3、文档名

HD2AV_F1.doc

二、视频分辨率率转换算法

1、内容

学习现有的分辨率转换算法,并根据各个算法的优劣选取最优的算法。

2、进度计划

(1)时间节点:2014/12/15~2014/12/17

(2)进展进度:已完成

3、文档名

HD2AV_F2.doc

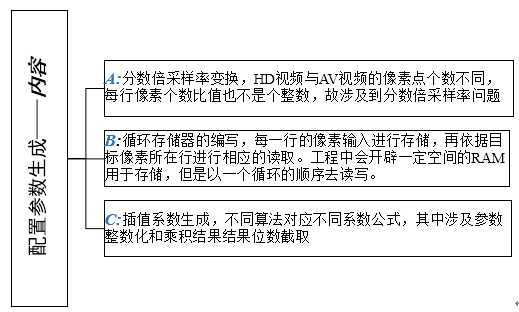

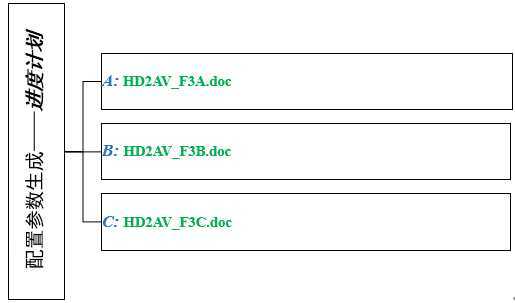

三、分辨率转换配套相关知识

采用不同的分辨率转换算法时,会需要一切相应的算法去配合实现,如下所示。

1、内容

2、进度计划

3、文档名

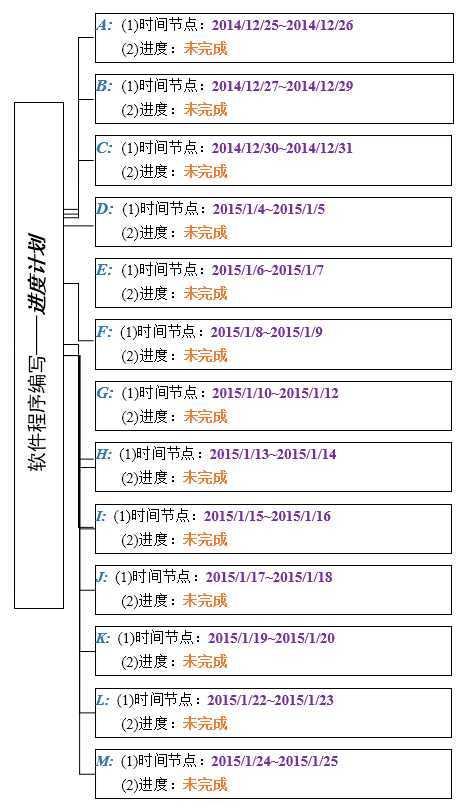

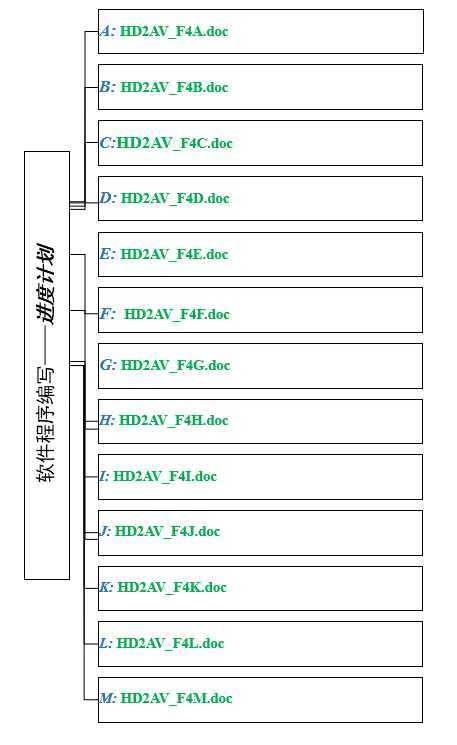

四、工程设计

1、内容

A:高清视频信号检测,剔除场消影行消影等无用信息,将有用视频像素存储(HD_Detect);

B:写行数据控制模块编写,实现将一行有效的像素存入一个LineBuf中(LineBuf_WriteCtr);

C:读行数据控制模块编写,实现依据行分辨率转换倍数去实现行数据读取(LineBuf_ReadCtr);

D:行缓存模块编写,通过写控制模块控制行数据写入,通过读控制模块控制行数据读出(LineBuf);

E:目标像素行模块编写,将行缓存模块输出数据乘上双三次插值系数,得出目标像素行(LineBuf_Coeff);

F:A~E部分的测试程序的编写,输入仿真视频信号以及行同步等,对比输出的目标行像素值是否正确(LineBuf_WriteCtr_tb);

G:写像素数据控制模块编写,实现将生成的目标行像素中1个像素点存入一个PixelBuf中(PixelBuf_WriteCtr);

H:读像素数据控制模块编写,实现依据列分辨率转换倍数去实现像素数据读取(PixelBuf_ReadCtr);

I:像素缓冲模块编写,通过写控制模块控制像素数据写入,通过读控制模块控制像素数据读出(PixelBuf);

J:目标像素模块编写,将像素缓冲模块输出像素值乘上双三次差值系数,得到最终的目标像素(PixelBuf_Coeff);

K:标清视频信号生成,将最终生成的目标像素按照标清AV信号的时序规则进行打包,并最终输出(AV_Generate);

L:G~K部分的测试程序编写;

M:读将程序编译并下载到实际电路中,使用ChipScope进行在线仿真调试。

2、进度计划

3、文档名

标签:

原文地址:http://www.cnblogs.com/sunxuxu/p/4184239.html