标签:

内存分页机制(memory paging mechanism)是从386开始的。线性地址通过分页机制透明转换为物理地址。

线性地址(linear address)为程序产生的地址;

物理地址(physical address)为程序访问的实际存储器地址。

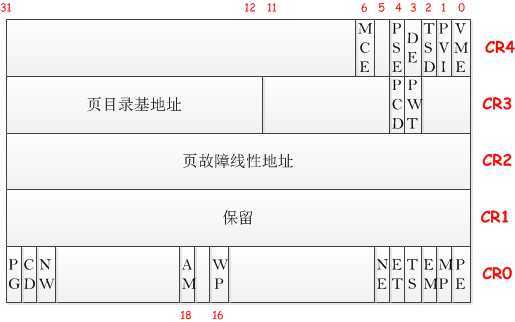

与分页机制相关的寄存器有CR0、CR1、CR2、CR3和CR4,且都是32位寄存器。

图一 控制寄存器

1. CR0的PG位为1时,分页启动。否则,线性地址即物理地址。在实模式和保护模式下分页机制都可工作。

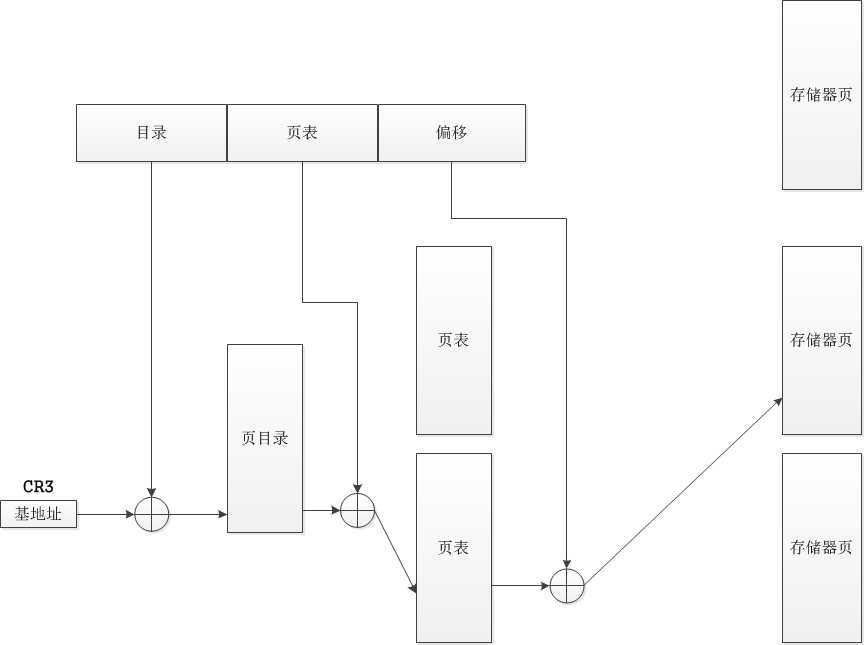

2. CR3包括页目录基地址以及PCD位和PWT位。如果PCD为1,则PCD引脚在非分页总线周期变为逻辑1,即允许外部硬件控制二级高级缓冲存储器。PWT位也在非分页总线周期作用在PWT引脚上,用于控制系统中的通写(write-through)高速缓冲存储器。页目录基地址用于为“页转换部件”寻址页目录。页大小一般为4KB。页目录包含1024个目录项,每项长4B。每个页目录项寻址一个包含1024项的页表。

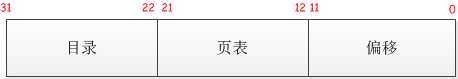

线性地址 = 页目录项(page directory entry) + 页表项(page table entry) + 存储器页偏移地址(page offset address)

图二 线性地址结构

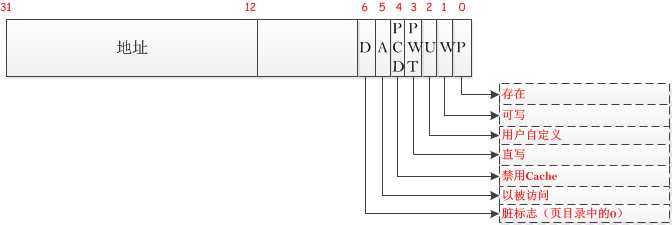

图三 页目录或页表项结构

TLB(translation look-aside buffer,转换后背缓冲区)是一个高速缓冲存储器。在80486中,TLB保存了32个最近使用的页转换地址。一般指令和数据高速缓冲存储器各有一个TLB。

在系统中只有一个页目录,页目录包含1024个双字地址,最多可以寻址1024个页表。页目录和每个页表的长度均为4KB。如果为4GB的内存分页,系统会为页目录分配4KB的存储空间,会为1024个页表分配1024*4KB=4MB的存储空间。

图四 分页机制示意图

标签:

原文地址:http://www.cnblogs.com/AmitX-moten/p/4199061.html