标签:

前几天写verilog的时候遇到这个问题,以前没有注意到这个问题,真是不应该!

举例:

贴一段很简单的代码

module async(clk,rst_n,out);

input clk,rst_n;

output[7:0] out;

reg[7:0] out;

//async

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out <= 8‘h00;

else

out <= out + 1‘b1;

end

//sync

//always @(posedge clk) begin

// if(!rst_n)

// out <= 8‘h00;

// else

// out <= out + 1‘b1;

// end

endmodule

综合出的电路不一样

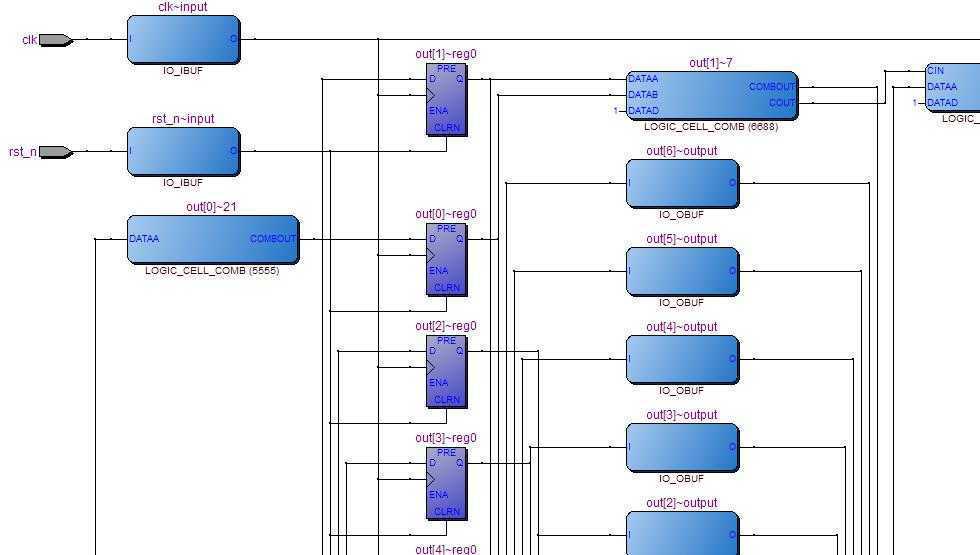

async

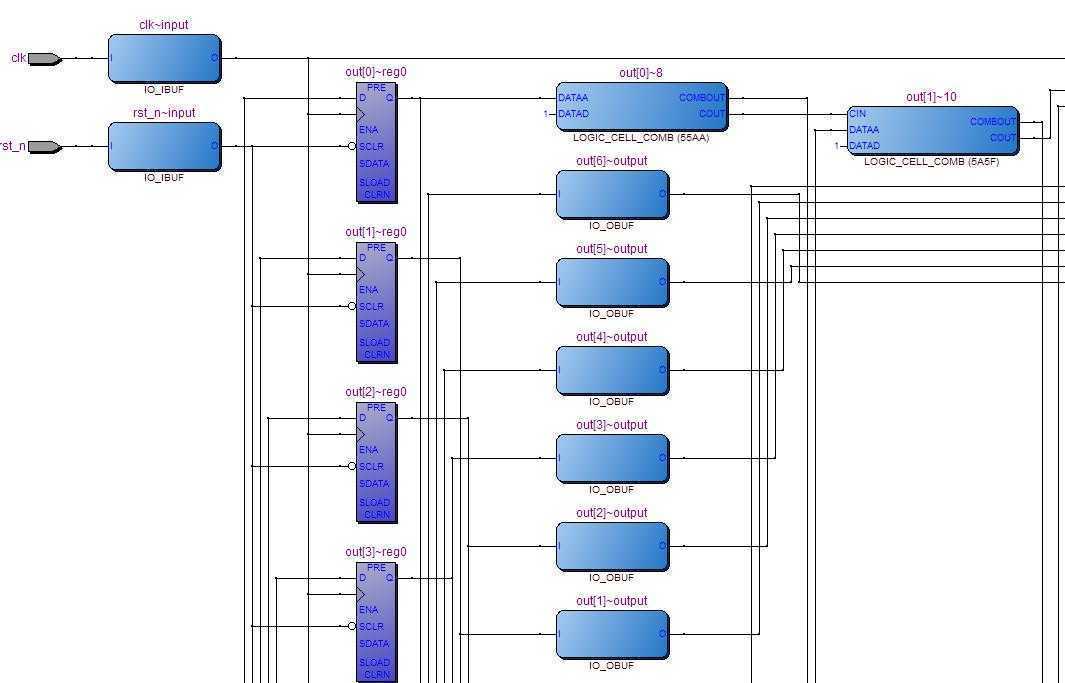

sync

总结:

在同步和异步电路设计过程中,异步电路,无论处于何种状态,触发器的输出端都会输出复位值,这是由fpga中触发器内部结构所决定的,说到底,复位电路这部分属于组合电路,然而同步设计中sclr只有在上升沿来临时方可进行输出,这种情况下,复位电路属于时序电路。在d触发器电路中pre代表输出1。clrn代表输出0。

标签:

原文地址:http://www.cnblogs.com/wqs131/p/4233166.html