标签:

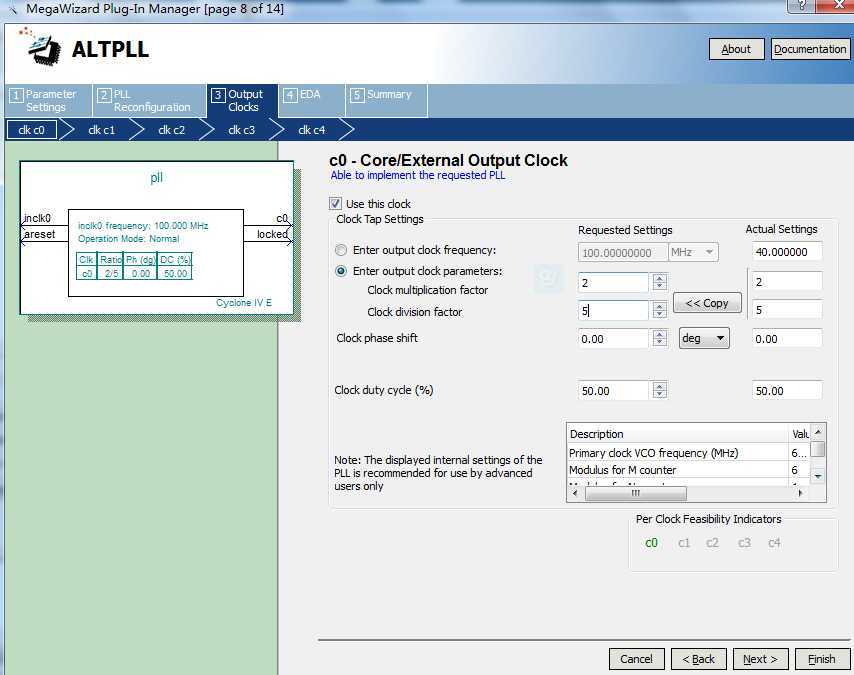

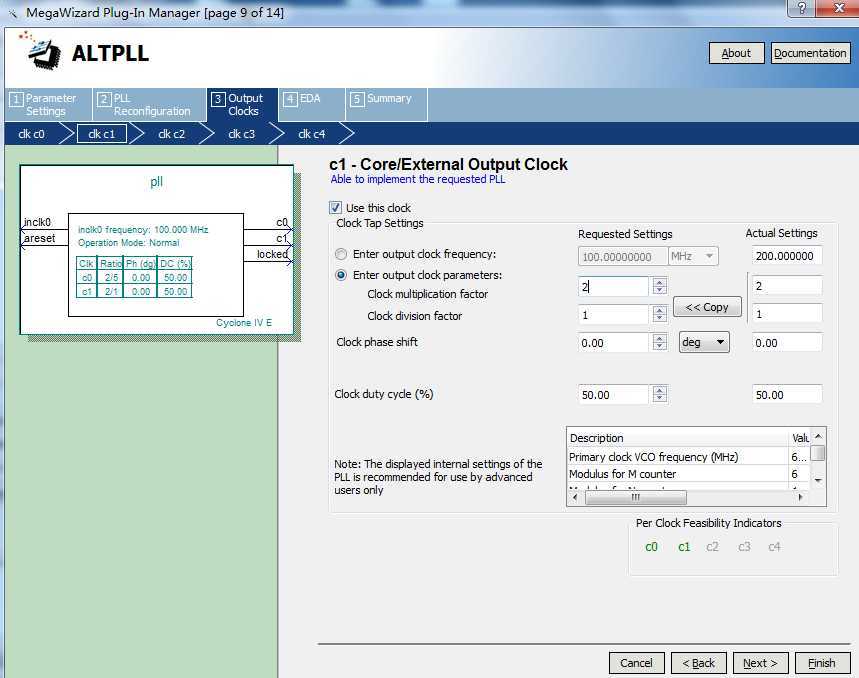

100mhz输入时钟,pll层40mhz和200zhm

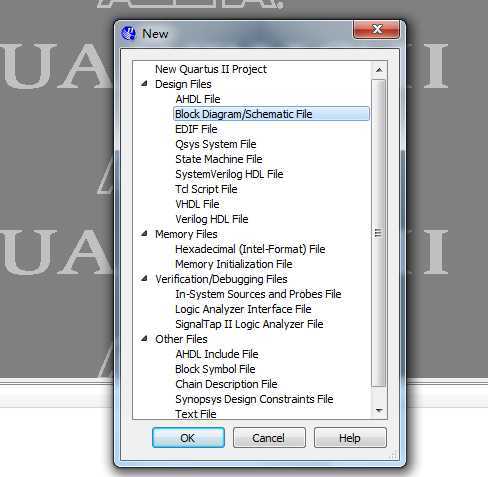

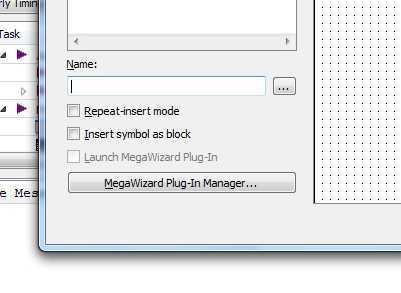

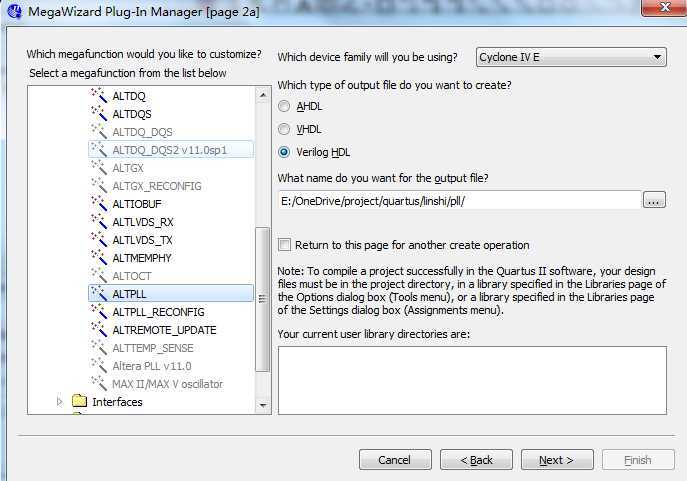

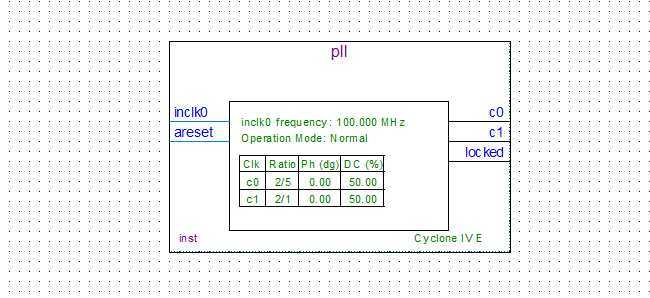

进入quartus,建立工程,新建图形文件,导入pll模块,设定pll相关参数。

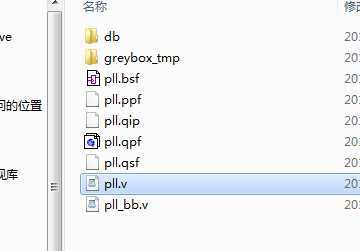

完成pll模块的建立,并生成pll.v文件

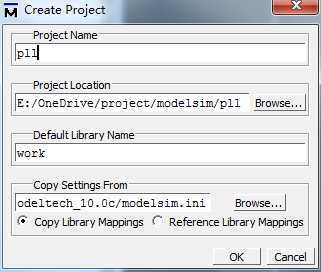

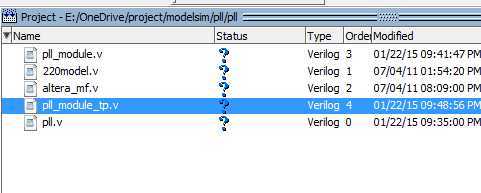

建立modesim工程

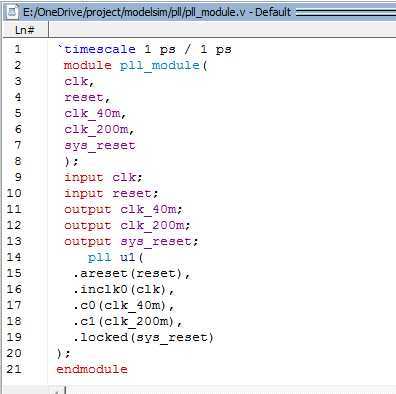

对pll模块进行打包

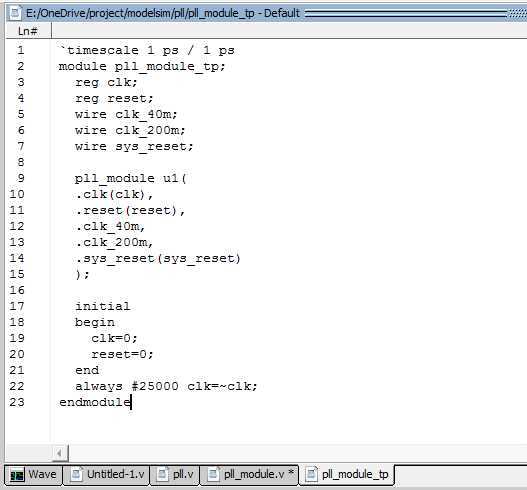

建立激励文本pll_module_tp

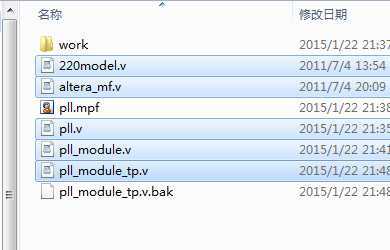

这样,modesim工作目录中除了pll.v, pll_module.v, pll_module_tp文件外,还需加入alter仿真库文件(如果modesim软件添加过alter库,这不需要)

进行编译

编译完成后,simulation-start simulation,选中仿真文件(本例中需取消enable optimization,我也还不知道为什么)

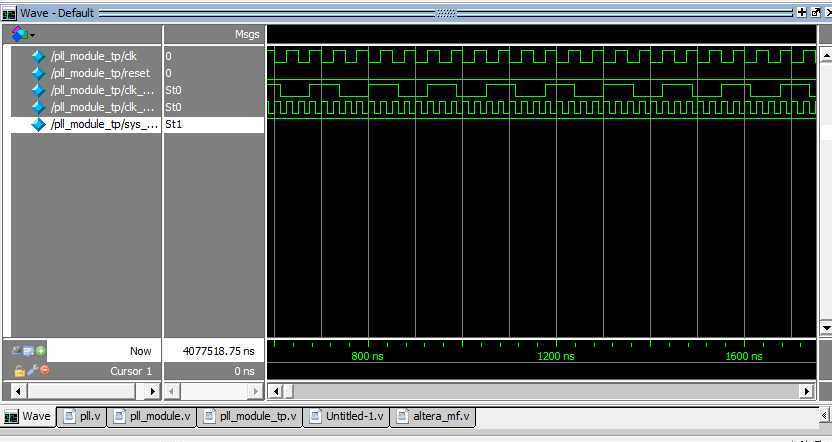

run 运行仿真

标签:

原文地址:http://www.cnblogs.com/shaogang/p/4242849.html