标签:

以下内容来自Quartus II Handbook Version 13.1 Volume 3: Verification /Section II. Timing Analysis

6. Timing Analysis Overview

Comprehensive static timing analysis involves analysis of register-to-register, I/O, and asynchronous reset paths.

综合的静态时序分析对象包括:寄存器-寄存器,I/O,及异步复位路径。

Timing analysis with the TimeQuest Timing Analyzer uses data required times, data arrival times, and clock arrival times to verify circuit performance and detect possible timing violations.

TimeQuest根据“数据要求时间” data required times,“数据到达时间”data arrival times和“时钟到达时间”clock arrival times来验证电路性能,检测可能的时序违规timing violations。

The TimeQuest analyzer determines the timing relationships that must be met for the design to correctly function, and checks arrival times against required times to verify timing.

TimeQuest确定时序关系,将“到达时间”和“要求时间”进行核对来验证时序关系是否满足。

需要特别指出的一点是:由于时序分析是针对时钟驱动的电路进行的,所以分析的对象一定是“寄存器-寄存器”对。在分析涉及到I/O的时序关系对时,看似缺少一个寄存器分析对象,构不成“寄存器-寄存器”对,其实是穿过FPGA的I/O引脚,在FPGA外部虚拟了一个寄存器作为分析对象。 riple

This chapter is an overview of the concepts you need to know to analyze your designs with the TimeQuest analyzer.

一、TimeQuest Terminology and Concepts 术语和概念

| 术语 | Definition |

| 结点 nodes | 最基本的时序网表单元. 表示 ports, pins, registers. |

| 单元 cells |

LUT,DSP模块,存储器模块,I/0单元,等等。 |

| 引脚 pins | cells的输入和输出 |

| 网络nets | pins之间的连接 |

| 端口ports | 顶层模块的输入和输出,比如设备的引脚 |

| 时钟clocks | Abstract objects representing clock domains inside or outside of your design. |

1、时序网表和时序路径

The TimeQuest analyzer requires a timing netlist to perform timing analysis on any design.

TimeQuest需要一个时序网表来进行时序分析。

After you generate a timing netlist, the TimeQuest analyzer uses the data to help determine the different design elements in your design and how to analyze

timing.

在产生时序网表之后,TimeQuest根据网表数据来确定电路中包含的设计单元,以及如何进行时序分析。

(1)时序网表

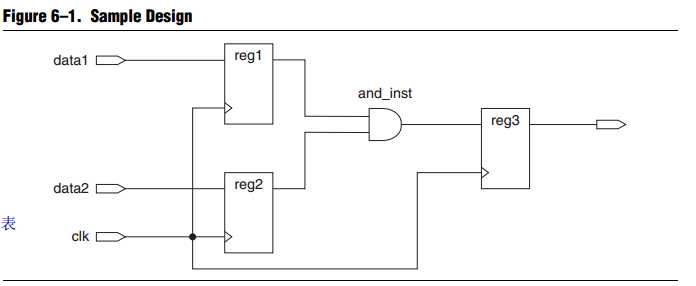

Figure 6–1shows a sample design for which the TimeQuest analyzer generates a timing netlist equivalent.

下图为一个采样电路,TimeQuest为这个电路生成了一个对应的时序网表。

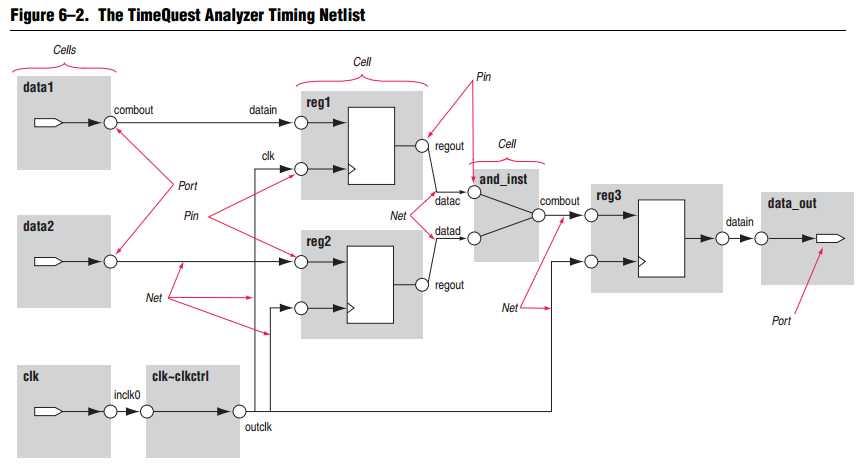

Figure 6–2shows the timing netlist for the sample design in Figure 6–1, including how different design elements are divided into cells, pins, nets, and ports.

下图为上图电路对应的时序网表,包含了如何将不同的设计单元分割成cells,s, pins, nets, ports.

(2)时序路径

Timing paths connect two design nodes, such as the output of a register to the input of another register.

时序路径连接2个设计结点nodes,比如从寄存器的输出到另一个寄存器的输入。

Understanding the types of timing paths is important to timing closure and optimization.

理解不同类型的时序路径对于时序终止和优化是非常重要的。

The TimeQuest analyzer uses the following commonly analyzed paths:

■ Edge paths—connections from ports-to-pins, from pins-to-pins, and from pins-to-ports.

边沿路径: ports-to-pins、pins-to-pins、pins-to-ports

■Clock paths—connections from device ports or internally generated clock pins to the clock pin of a register.

时钟路径:从设备端口或者内部产生的时钟引脚到一个寄存器的时钟引脚。

■ Data paths—connections from a port or the data output pin of a sequential element to a port or the data input pin of another sequential element.

数据路径:从一个时序单元的一个端口或数据输出到 另一时序单元的输入输入引脚。

■ Asynchronous paths—connections from a port or asynchronous pins of another sequential element such as an asynchronous reset or asynchronous clear.

异步路径:从另一个

标签:

原文地址:http://www.cnblogs.com/qyl1999/p/4265481.html