标签:

通过缩短部分指令流水线级数,减少IO口变化及寄存器赋值,以达到降低动态功率的目的,首先对指令进行分类如下。

指令分类:

(1) IF ID EX MEM WB

LOAD

(2) IF ID EX MEM NOP

STORE JMPR BZ BNZ BN BNN BC BNC

(3) IF ID EX NOP WB

LDIH ADD ADDI ADDC SUB SUBI SUBC AND OR XOR SLL SRL SLA SRA

(4) IF ID NOP NOP NOP

CMP

(5) IF NOP NOP NOP NOP

JUMP(直接跳转)

(6) NOP NOP NOP NOP NOP

NOP

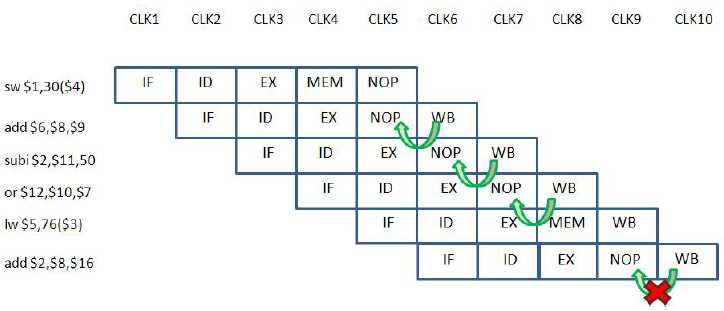

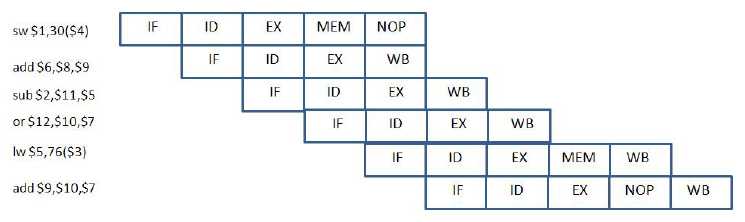

可看出,(3)类指令可将wb前移,略去流水线mem,因其对它无贡献。但是前移的前提条件是前面未出现(1)类指令,或(1)类指令被(2)(4)(5)(6)类指令刷除其作用。

优化模拟效果图如下:

模型转换为实际时,时序问题应理得非常清楚,判断状态值与EX同步,则需在ID对状态赋值,方可在EX时对其调用。

基本步骤如下:

(a)在ID内对状态进行初始化为lower(可降低功耗)状态,判断下一周期内指令即ex_ir是否为(1)类指令,若是,状态变为normal。若为(2)(4)(5)(6)类指令,状态变为power,否则状态不变;

(b)在ex_ir内判断当前指令是否为(3)类且状态为lower(与ID时获得此次状态),若是则传入mem内指令为NOP;

(c)在mem_ir内判断ex_ir是否为(3)类指令且状态为lower,若是则WB传入ex_ir,且将ALUo赋值给reg_C1,否则传入mem_ir。

参考:《Low-Power Pipelined MIPS Processor Design》

标签:

原文地址:http://www.cnblogs.com/Carlen/p/4273624.html