标签:

参考<STM32参考手册>

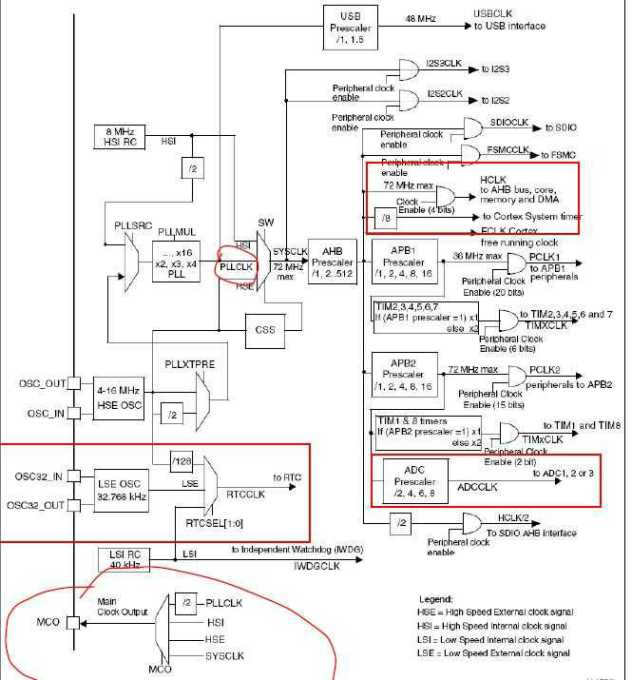

stm32时钟树:

当HSI被用于作为PLL时钟的输入时,SYSCLK的最大频率不得超过64MHz

stm32有以下四种时钟源(内部时钟源起振较快,刚上电时默认使用内部时钟源,外部时钟源叫稳定精确):

高速外部时钟(HSE):外部晶振产生8MHz的时钟,为系统提供更为精确的时钟.

高速内部时钟(HSI):由内部RC振荡器产生,频率为8MHz.

低速外部时钟(LSE):外部晶振产生32.768kHz的时钟,主要为实时时钟(RTC)模块提供低功耗且准确的时钟源.

低速内部时钟(LSI):有内部RC产生,主要供给RTC模块,频率约为40kHz.

a,左端的OSC_OUT和OSC_IN两个引脚接外部晶振的两端,从这里开始

b,8MHz的时钟进入分频器PLLXTPRE,通过寄存器配置选择对输入的时钟二分频或不分频,这里选择不分频

c,8MHz的时钟遇到开关PLLSRC,可以选择器输出为HSE或HSI,这里选择为HSE.紧接着进入锁相环PLL,这里我们选择倍频因子PULLMUL为9. 经过PLL的时钟称为PLLCLK,此时其频率为72MHz.

d,PLLCLK经过一个SW开关就是STM32的系统时钟(SYSCLK)了. 通过这个开关可以切换SYSCLK的时钟源为HIS,HSE,PLLCLK,我们选择PLLCLK

e,PLLCLK同时还流向了USB预分频,这个分频器输出为USB外设时钟(USBCLK)

f,SYSCLK经过AHB预分频器后,流向FCLK,HCLK,SDIOCLK(SDIO外设的时钟),FSMCCLK(存储器控制器FSMC的时钟)以及APB1和APB2预分频器的输入端,这里设置AHB分频器不分频.

g,GPIO外设挂载在APB2总线上,APB2的时钟是APB2预分频器的输出. 设置APB2预分频器不分频.

由上面的时钟树:

AHB和APB2域的最大频率是72MHz,APB1域的最大频率为36MHz,SDIO接口的时钟频率固定为HCLK/2

AHB时钟经8分频后供给Cortex系统定时器(SysTick)的外部时钟

ADC时钟由高速APB2时钟经2,4,6,8分频后得到

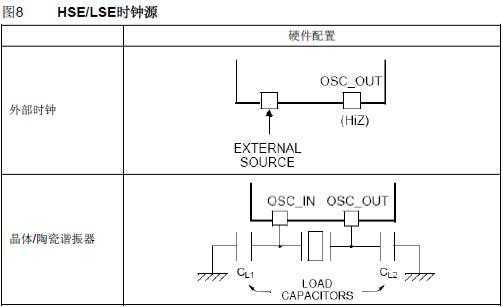

HSE和LSE可由以下两种时钟源产生(外部晶体/陶瓷谐振器和外部时钟),V5开发板采用的外部晶体/陶瓷谐振器

外部时钟源(HSE/LSE旁路)

在这个模式里必须提供外部时钟,外部时钟信号连接到OSC_IN,同时OSC_OUT悬空

HSE旁路,其最高频率可达25MHz.通过设置RCC_CR寄存器里的HSEBYP和HSEON位来选择这一模式.

外部晶体/陶瓷谐振器(HSE/LSE晶体)

HSE晶体可产生4-16MHz的时钟,在启动阶段当RCC_CR中的HSERDY位被硬件置1时,HSE时钟信号才被释放出来.可以通过设置RCC_CR中的HSEON来启动和关闭HSE晶体.如果在RCC_CIR中允许产生中断,将会产生相应的中断.

LSE晶体产生32.768kHz的时钟,在启动阶段当RCC_BDCR中的LSERDY被硬件置1时,LSE时钟信号才被释放出来.可以通过设置RCC_BDCR中的LSEON来启动和关闭LSE晶体.如果在RCC_CIR中允许产生中断,将会产生相应的中断.

这里只是做简单概括,详细情况请参考<STM32参考手册>

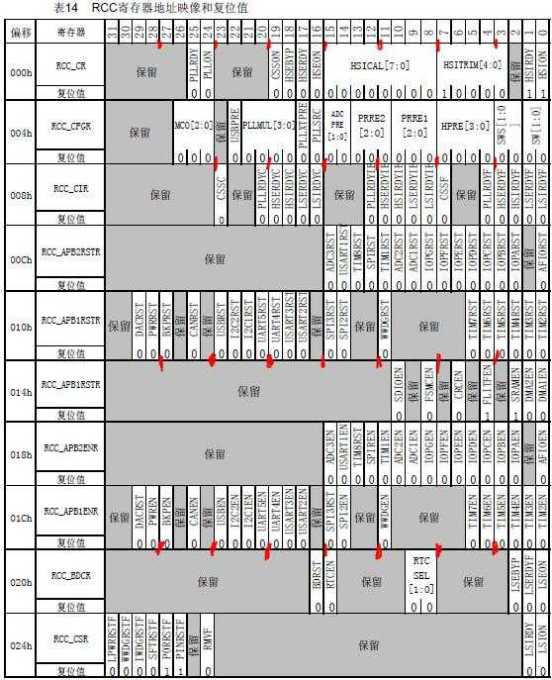

PLLRDY:PLL时钟就绪标志,PLL锁定后由硬件置1(PLL锁定)

PLLON:(1)PLL使能,由软件件置1或清零,当进入停止或待机模式时,由硬件清零

CSSON:(1)如果外部4-25MHz时钟就绪,时钟检测器开启

HSEBYP:(1)外部4-25MHz振荡器被旁路,即不使用外部晶振

HSERDY:(1)外部4-25MHz时钟就绪,由硬件置1.在HSEON位清零后,该位需要6个外部4-25MHz时钟周期清零

HSEON:(1)HSE高速振荡器开启,由软件置1或清零,当进入待机或停止模式时,由硬件清零,当HSE被用作系统时钟时,该位不能被清零

HSIRDY:(1)内部8MHz时钟就绪

HSION:(1)内部8MHz时钟开启,由软件置1或清零,当从待机和停止模式返回或用作系统时钟的HSE时钟发生故障时,硬件置1.

USBPRE(USB预分频):(0)PLL时钟1.5分频作为USB时钟,(1)PLL直接作为USB时钟,由软件置1或清零来产生48MHz的时钟,在RCC_APB1ENR寄存器中使能USB之前,需保证该位已经有效

PLLMUL:PLL倍频系数,只有在PLL关闭的情况下才能写入

PLLXTPRE:(1)HSE二分频后进入PLL,只有在PLL关闭时才能写入

PLLSRC:(1)HSE作为PLL输入时钟,(0)HSI时钟二分频后作为PLL输入时钟

ADCPRE(ADC预分频):配置PCLK2经过2,4,6,8,16分频后作为ADC时钟

PPRE2(高速APB预分频):配置HCLK经过1,2,4,8,16分频后作为APB2总线时钟(PCLK2)

PPRE1(低速APB预分频):配置HCLK经过1,2,4,8,16分频后作为APB1总线时钟(PCLK1)

HPRE(AHB预分频):配置SYSCLK经过1,2,4,8,16,64,128,256,512分频

SWS:指示哪个时钟源被作为系统时钟,由硬件置1清零

SW:选择系统时钟源(HIS,HSE,PLL),当从待机或停止模式返回或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择HSI作为系统时钟(如果时钟安全系统已被启用)

CSSC:(1)清除CSSF安全系统中断标志位CSSF (0)无效

PLLRDYC:(1)清除PLL就绪中断标志位PLLRDYF (0)无效

HSERDYC:(1)清除HSE就绪中断标志位HSERDYF (0)无效

HSIRDYC,LSERDYC,LSIRDYC:与上一个类似

PLLRDYIE:(1)PLL就绪中断使能 (0)PLL就绪中断关闭

HSERDYIE,HSIRDYIE,LSERDYIE.LSIRDYIE:与上一个类似

CSSF:外部4-25MHz振荡器时钟出现故障时,由硬件置1,由软件通过置1 CSSC位来清除

PLLRDYF:在PLL就绪且PLLRDYIE位被置1时,由硬件置1,由软件置1 PLLRDYC位来清除

HSERDYF,HSIRDYF,LSERDYF,LSIRDYF:与上一个类似

AFIORST:(1)复位辅助功能 (0)无作用 软件置1清零

IOPARST,IOPBRST,IOPCRST,IOPDRST,IOPERST,IOPFRST,IOPGRST:(1)复位相应的端口,(0)无作用

TIM1RST,TIM8RST:复位TIMx定时器

USART1RST,SPI1RST,ADC1RST,ADC2RST,ADC3RST:(1)复位相应接口 (0)无作用

TIM2RST,TIM3RST,TIM4RST,TIM5RST,TIM6RST,TIM7RST:(1)复位相应寄存器 (0)无作用

SPI2RST,SPI3RST,USART2RST,USART3RST,USART4RST,USART5RST,I2C2RST,I2C1RST,USBRST,CANRST

DACRST:(1)复位DAC接口

PWRRST:(1)复位电源接口

BKPRST:(1)复位备份接口

WWDGRST:(1)复位窗口看门狗

SDIOEN:(1)SDIO时钟开启,由软件置1清零

FSMCEN:(1)FSMC时钟开启

CRCEN:(1)CRC时钟开启

FLITFEN:(1)睡眠模式时闪存接口电路时钟开启

SRAMEN:睡眠模式时SRAM时钟开启

DMA2EN,DMA1EN:(1)DMAx时钟开启

AFIOEN:(1)辅助功能IO时钟开启

IOPAEN,IOPBEN,IOPCEN,IOPDEN,IOPEEN,IOPFEN,IOPGEN,ADC1EN,ADC2EN,ADC3EN,TIM1EN,TIM8EN,

USART1EN,SPI1EN:相应的接口时钟开启,由软件置1清零

DACEN,PWREN,BKPEN,CANEN,USBEN,I2C2EN,I2C1EN,UART5EN,UART4EN,USART3EN,USART2EN,SPI3EN,

SPI2EN,WWDGEN,TIM7EN-TIM2EN:相应接口时钟开启,由软件置1清零

只能由备份域复位有效复位为0x0000 0000

注意:(1)一旦连续对该寄存器访问,等待状态将被插入

(2)该寄存器中的LSEON,LSEBYP,RTCSEL,RTCEN处于备份域,因此这些位在复位后被写保护,只有在电源控制寄存器(PWR_CR)中的DBP位置1后才能对这些位改动,只能由备份域复位或VBAT上电复位.

BDRST:(1)复位整个备份域,软件置1清零

RTCEN:(1)RTC时钟使能 RTCSEL[1:0]:RTC时钟源选择

LSEBYP:(1)LSE时钟被旁路 LSEON LSERDY:硬件置1

复位标志位由电源复位清除,其他标志位由系统复位清除;一旦连续对该寄存器进行访问,等待状态将被插入

LPWRRSTF(低功耗复位标志):在低功耗管理复位发生时由硬件置1;由软件通过写RMVF位清除

WWDGRSTF:在窗看门狗复位发生时由硬件置1;由软件写RMVF位清除

IWDGRSTF:独立看门狗复位发生在VDD区域时由硬件置1;由软件写RMVF位清除

SFTRSTF(软件复位标志) PORRSTF(上电/掉电复位标志) PINRSTF(NRST管脚复位标志)

RMVF:(1)清除复位标志 (0)无作用

LSION(内部低速振荡器使能) LSIRDY 硬件置1清零

在开启外设时钟前先配置系统时钟,由SystemInit()函数配置系统时钟

启动文件中,在进入main函数之前调用了SystemInit()函数:

IMPORY SystemInit

LDR R0,=SystemInit

BLX R0

SystemInit()函数在对相应的寄存器进行复位后调用SetSysClock(),然后根据定义了的宏SYSCLK_FREQ_72MHz调用函数SetSysClockTo72()将SYSCLK设置为72MHz(前提是外部时钟源HSE的振荡频率为8MHz)

通过调用RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD|RCC_APB2Periph_CPIOB, ENABLE)来开启GPIOB和GPIOD的外设时钟.

Cortex-M3有32根地址线,寻址空间为4GB.ARM公司设计时将从0x40000000到0x5fffffff(512MB)的地址分配给片上外设,将片上外设的寄存器映射到这个地址上.称0x40000000为外设基地址

stm32芯片有AHB,APB,APB2总线,挂载在这些总线上的设备有特定的地址范围,在stm32f10x.h中有如下定义:

#define PERIPH_BASE ((uint32_t)0x400000000)

#define APB1PERIPH_BASE PERIPH_BASE

#define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)

#define AHBPERIPH_BASE (PERIPH_BASE + 0x20000)

标签:

原文地址:http://www.cnblogs.com/zhoutian220/p/4276414.html