乒乓操作的优势:

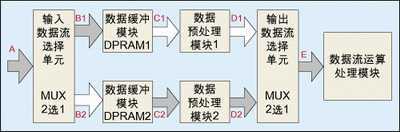

第三点的实现方式:(实例)

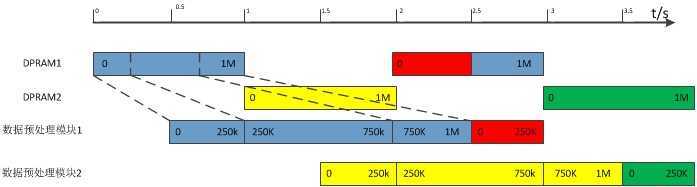

A端输入速率1Mbps的信号,DPRAM存储量大于1M bit,数据流运算处理模块的处理速度为1 Mps,数据预处理模块1&2的处理速度是0.5 Mbps;

以数据缓冲模块DPRAM1为主(DPRAM2实现方式相同),进行乒乓操作:

信号输入 2选1输入数据流选择单元,第一个操作周期(T = 1 s),执行B1,数据送入DPRAM1,在t = 0.5s绝对时间时,DPRAM1中已经存储500K bit 数据,数据预处理模块1开始从DPRAM1的零地址开始读取数据;当t = 1 s时,DPRAM1中存储了1M bit的数据,数据预处理模块1读取了250K bit的数据,B1操作停止,输入数据流选择单元选择B2操作,当t = 2 s时,DPRAM2存储了1M bit数据,数据预处理模块1从DPRAM1中读取到了750K bit数据,输出数据流选择D1(周期为1s),输入数据流再次选择单元选择B1,开始B1操作;这时A输入的数据开始从DPRAM1 的零地址处覆盖原有数据,当t = 2.5 s时,数据预处理模块1 共计用时0.5+1.0+0.5=2s,读取了1M bit,而DPRAM1中的数据刚好被覆盖了500K bit数据,这时数据预处理模块1又从DPRAM1的零地址开始读数据,开始新的循环;

未完待续........

原文地址:http://www.cnblogs.com/zqlxinyu/p/3760659.html