标签:

SPI, Serial Peripheral Interface, 串行外设接口, 是一种高速的、全双工、同步的通信总线

SPI在芯片的管脚上只占用四根线

SPI接口主要用于MCU与各种外围设备以串行方式进行通信以交换信息

外围设备包括EEPROM、FLASH、实时时钟、AD转换器、数字信号处理器和数字信号解码器中

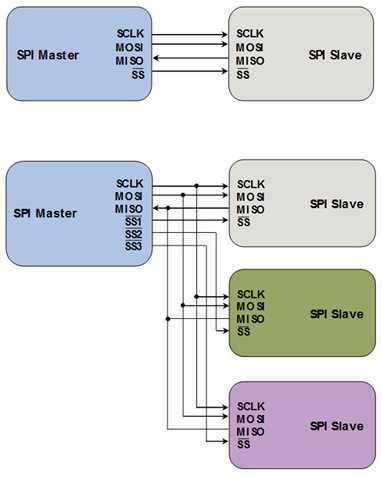

它以主从方式工作, 通常有一个主设备和一个或多个从设备

下图是SPI常用的两种场景

SPI通常有四组信号线

- SCLK : Serial Clock(自master输出) - MOSI/SIMO : Master Output, Slave Input(自master输出) - MISO/SOMI : Master Input, Slave Output(自slave输出) - SS : Slave Select(低电平有效;自master输出)

另一种称呼亦广泛被使用

- SCK : Serial Clock(自master输出) - SDI/DI/SI : Serial Data In - SDO/DO/SO : Serial Data Out - nCS/CS/nSS/STE : Chip Select, Slave Transmit Enable(低电平有效;自master输出)

在SPI中,数据是同步进行发送和接收的, 数据传输的时钟基于来自Master的时钟脉冲

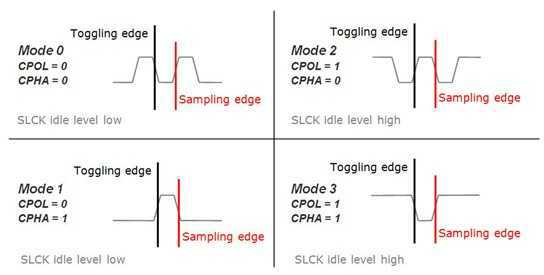

最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA), 它们决定了数据取样的时钟沿

- 时钟极性(CPOL): 定义SPI串行时钟的活动状态,

CPOL=0表示时钟开始值是低电平,所以第一阶段(前沿)的时候会处在上升沿,第二阶段(后沿)是下降沿

CPOL=1表示时钟开始是高电平,所以第一阶段(前沿)就是下降沿;

- 时钟相位(CPHA): 定义相对于数据位的时钟相位, 用于采样数据,

CPHA=0表明在前沿期间进行采样; CPHA=1表明在后沿进行采样

tip: 关于CPOL和CPHA, 请参考<详解SPI中的极性CPOL和相位CPHA>

基于CPOL和CPHA的组合SPI有四种工作模式

不同工作模式下时序图是不同的,但这又是设备相关的,此处不介绍

参考

<SPI子系统分析>

<SPI Block Guide V3>

<嵌入式设备中的FLASH>

标签:

原文地址:http://www.cnblogs.com/hzl6255/p/4298998.html