标签:

1.异步复位

always @ ( posedge sclk or negedge s_rst_n )

if ( !s_rst_n )

d_out <= 1‘b0;

else d_out <= a;

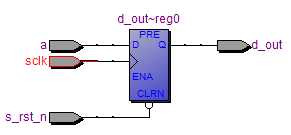

综合出来的RTL视图如下所示:

从图中可以看到寄存器d_out有一个低电平有效的复位信号s_rst_n端口,即使设计是高电平复位,实际综合后也会把异步复位信号反向后接到这个CLRN端;

从图中可以看到寄存器d_out有一个低电平有效的复位信号s_rst_n端口,即使设计是高电平复位,实际综合后也会把异步复位信号反向后接到这个CLRN端;

2.同步复位

always @ ( posedge sclk )

if ( !s_rst_n )

d_out <= 1‘b0;

else d_out <= a;

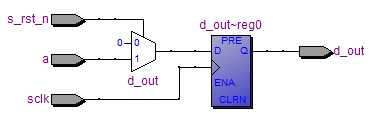

综合出来的RTL视图如下所示:

从图中可以看到,同步复位没有用到寄存器的CLRN端口,只是把复位信号s_rst_n作为输入逻辑信号,这样相对于异步复位,就增加了FPGA内部的逻辑资源消耗;

从图中可以看到,同步复位没有用到寄存器的CLRN端口,只是把复位信号s_rst_n作为输入逻辑信号,这样相对于异步复位,就增加了FPGA内部的逻辑资源消耗;

3.异步复位VS同步复位

它们各有优缺点,FPGA内部的寄存器有支持异步复位的专用端口,采用异步部位无需增加器件的额外逻辑资源,但异步复位也存在隐患,容易产生亚稳态问题;同步复位在时钟信号sclk的上升沿触发时进行系统是否复位的判断,这降低了亚稳态出现的概率(只是降低,不可能完全避免);

标签:

原文地址:http://www.cnblogs.com/geekite/p/4337256.html