本文主要分享研究生期间所学到的一些科研和项目经验,实践部分偏重于硬件电路。点滴琐碎,还请见谅。

模块通用性:基本思想是做通用可扩展、特定功能的小“模块”,而不要在后续阶段为加入功能而添加代码。

模块就是你给我输入,我给你想要的输出,仅此而已,尽可能不要让我进行控制。

模块化,减少耦合度,便于移植和调试。尽量模块化,可避免大的改动。

【注】自己编写的三分频模块在Modelsim里会仿真出什么结果呢?比如clk_sn由75M时钟clk_sf三分频产生,那么仿真出来的clk_sn为42ns的时钟,而不是40ns(25M)——因为你所加的75M时钟仿真激励不可能很精确(13.333...ns)!

- 把FPGA仿真结果数据导入Matlab中,画出Matlab理论曲线与FPGA仿真曲线比较(大数据量)

- 提出一种想法后务必画出理论比较曲线(有比较才有说服力),过多的解释说明倒不如图表直观。

- 设计验证机制

勤写报告:1. 保持进度; 2. 用于提问讨论; 3.论文素材。

三种报告:

1) 给老师的报告:综合、轮廓、整体思路——图表化

2) 给自己的报告:设计算法、心得经验、调试细节

3) 给接收人的报告:系统、思路、如何实现及该做哪些工作,便于迅速上手。

以后发挥自己的能动性,每天向老师汇报进度——不是做了多少(太“虚”),而是具体完成了什么!

计划、讨论、汇报,讲给老师听。

有问题一定写文档问老师,不要想着口头说——这其实减少了仔细思考的过程。

不合理的现象背后,一定有合理的原因。只有抱定这一信念,才能解决调试中遇到的各种问题。与此相反的是:遇到不合理的现象,不是去寻求合理的解释,而是猜想有一些不可控、不可证明的原因。比如猜想综合工具有bug,电路的信号完整性有问题,芯片过热等。这样一想,问题往往不了了之,调试也就半途而废了。

遇到问题首先思考什么情况下会产生此类问题,寻求可能原因,而不是怀疑软/硬件工具有问题。

1) 设计目标分析

主要确定芯片应当完成哪些基本功能,以及分析未来可能要增加的功能。注意选择器件时要留有足够的设计余量,以保证今后升级时单板不会因此而修改。

2) 功能模块划分

让设计层次分明条理清晰。另外在确定功能模块划分过程中,能使设计者在总体上考虑芯片的各个问题,发现一些比较深层次的问题。

3) 确定关键电路时序和模块间接口时序(总体方案)

事实上,在功能模块划分过程中就必须考虑时序方面的问题。有时,在确定设计目标时就得考虑关键电路时序。

在此前的设计过程中,我们是将项目设计进行功能分解之后,立刻着手子模块具体电路设计,最后再进行系统联调,出现问题了再去更改设计。这是在凑电路,而不是在设计电路。

设计电路,尤其是数字电路,最关键的一环就是:设计各模块间的接口时序,确定关键电路的时序。在做总体方案时,应深入到模块间的时序划分,关键电路的时序确定,并以此作为指导来进行设计。

“时序是事先设计出来的,而不是事后测出来的,更不是凑出来的。”

4) 具体电路设计(并写出详细设计文档)

在进行模块设计时,应先画出每个模块的原理结构,而后画出其工作原理时序图,在工作原理时序图的指导下进行具体电路设计。即“先时序后电路”的设计方法。在条件允许范围内,尽量用集成度高的电路语言直接表述。

设计流程:明确模块的原理功能-->画出时序图-->(映射为逻辑电路)-->用硬件语言描述时序图(或电路映射图)——先时序后电路!

5) 调试验证(仿真测试方案)

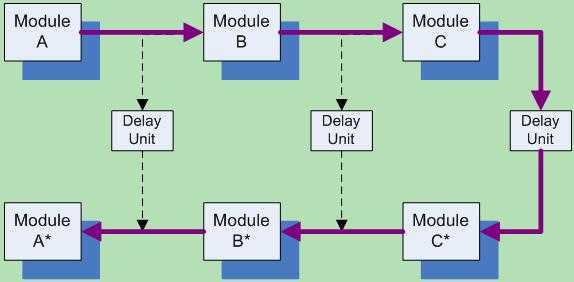

设计时就应该做好测试验证机制。我们目前所采用的验证机制为“隔离”(回路之间加入不同的延迟单元,测试时序是否满足)、“直通”(模块直连,如调制数据直接送往解调模块——bypass同步)。示意图如下:

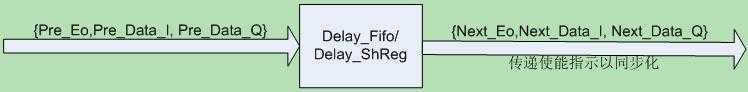

其中延迟单元Delay Unit结构如下:

由于时钟建立-保持时间的限制,FPGA设计中应尽量避免采用多时钟网络,或尽量减少时钟的个数。尽量避免采用多个时钟,多使用触发器的使能端来解决。

为了避免异步的时钟域产生错误的采样电平,一般使用RAM、FIFO存储的方法完成异步时钟域的数据转换,在输入端口使用上一级时钟写数据,在输出端口使用本级时钟来读数据,能够非常方便地完成异步时钟域之间的数据交换。

处理速度与面积问题的原则:向关键路径部分要时间,向非关键路径部分要面积。为了获得更高的速度,应当尽量减少关键路径上的逻辑级数;为了获得更小的面积,应当尽量共享已有的逻辑电路。

以寄存器为边界划分工作模块。在设计较大规模的电路时,分模块设计是必不可少的,在各模块通过之后再进行系统的联调。但由于在单模块调试和联调时布线资源的占用紧张程度不同,使得每个模块的输出无法保持与单独布线时相同,在联调时造成困难。如果每一个模块的输出端口都采用寄存器输出,那么即使在整体布局布线后,各模块的输出依然可以保证原来的时序,这使得联调的工作效率大大提高。加入这些寄存器也使得电路的可测性有所提高。

1) 将HDL文件或bdf文件设为顶层

2) Processing | Start | Start Analysis & Synthesis及Start Fitter生成post-fitting节点

3) 建立vwf波形文件加入节点和激励

4) Simulation Tool | Functional | Generate Functional Simulation Netlist | Start

修改v文件后再次仿真时,只需要Generate Functional Simulation Netlist即可。而生成网表后,除重新编译源文件外,每次修改.vwf波形后都不必重新生成网表。

功能仿真时不计入器件延时,但经过寄存器后必产生一个周期的“延时”,这不同于器件延时,因为它本质上与时钟节拍相关,并非器件或布线固有延时。

Quartus仿真时最好让CLK有效沿采到输入数据的中间(稳定),这样无论Functional还是Timing仿真,都不会出现采样问题。如果输入数据在CLK有效沿变化,则Functional仿真会向后采,而Timing仿真会向前采。中间变量均向前采。似乎Quartus功能仿真时默认下降沿锁存数据,上升沿驱动输出,而modelsim均取上升沿。

End Time尽量设大一些,免得输出延时太大导致波形显示不全,而重新设置初始化文件既不方便又容易出错。当然End Time大了,仿真时间会长一点,但总好过因End Time不够而被迫重新编辑波形。End Time比较大时,时间轴Time bar的移动很不方便,可以在波形需要读取坐标处右键“Insert Time bar”。如果此前已有其他Time bar,则在新Time bar(虚线)上右键“Make Master Time bar”设为主坐标(实现),便可通过键盘“←”、“→”键调整坐标位置。记录下目标点的大致坐标,观察时直接拖动水平滚动条更快。直接在信号波形上双击,即可选中整个波形。选择一段波形,再鼠标滚轮放大,则以选中波段为中心显示放大。Tools|Options|Processing里可以设置仿真输出格式为vwf、cvwf或vcd。

v文件设为顶层后File-->Create/Update...即可生成symbol,但建议先做...Elaboration过滤语法错误。bdf文件更新及转HDL文件时无需设为顶层。改变源文件端口次序可使生成的符号易于连线。bdf生成的HDL文件智能化不够,底层模块修改参数后注意要在HDL中一定要改过来!

在图表文件里双击symbol可以打开其对应的v文件或bdf文件或Select对话框。如果同时还有对应的vwf文件加入工程,也会将其列入对话框中。

在Quartus里打开已锁定管脚的图表文件,有时会发现未显示管脚,这时需将该图表文件设为顶层文件(注意从Project Navigator中剔除与其对应或重名的.v文件),再Start Analysis and Elaboration即可在图表文件中显示已分配过的管脚。

用MegaWizard定制元件,其实只需生成.v和.bsf两种格式的文件。除非定制ROM(需指定内存初始化文件),否则类似的宏单元没必要重复定制,其实只需例化名不同即可。比如经常要定制I、Q两路的FIFO,其实只需定制一个,在例化名里标识出I、Q即可。在Project Navigator-->Hierarchy里宏单元名上右键“MegaWizard Plug-in Manager”或直接双击,可打开宏单元编辑器修改定制元件。如果Hierarchy 不能展开,设置顶层并Start Analysis and Elaboration即可。

Quartus II停止响应时,直接关掉重启。如果上次编译后未做修改,则重新打开工程后不必再编译一遍。但不要因为编译后重新打开工程不必再次编译,而不必要地重启工程或重启Quartus。因为重启后再也无法Undo此前所做的修改了,而这可能带来非常大的麻烦。

3.4 Quartus中调用Modelsim做仿真

1) 功能仿真

将图表文件转换为HDL文件,然后将.v文件加入工程并设为顶层(同时剔除.bdf文件),在Settings里设置testbench路径,Start Analysis and Elaboration无误后Run EDA RTL Simulation,否则会出现Module “xxx” is not defined的错误。

2) 时序仿真

步骤基本同上,只不过最后要选Run EDA Gate Level Simulation。

仿真ROM时,要将.hex文件放置在simulation/modelsim目录下。

Modelsim中显示模拟波形:信号名上右键“Properties”-->“Format”-->“Analog”选项卡,Height设为50(默认17),Offset设为0,Scale设为0.1。

如果你的程序复杂,时钟频率高,测试向量多都会导致较长的Modelsim仿真时间,这是难以避免的。当然有一些小技巧可以在一定程度上缩短仿真时间(不考虑是否改善计算机硬件配置)比如设计的工作时钟频率为80MHz,即周期为12.5ns,原则上同步时序电路进行功能仿真的时间步进单位就是6.25ns,timescale为0.01ns因为同步时序逻辑一般都只使用时钟的上升沿 所以不需要严格要求时钟其他指标的具体实现 这样就可以把时钟信号设置为非1:1的占空比 即高电平6.5ns 低电平6ns 此时的timescale变为0.1ns 仿真速度可以加快一些 另外如果通过让testbench输出仿真结果文件而不是直接察看波形窗口的话 仿真速度可有较明显提高。

timescale在仿真的时候需要注意:

1) 如果不设置,modelsim默认1ps/1ps,vcs默认1s/1s

2) 可通过printtimescale打印出来指定模块的timescale,如下

1 Initial begin 2 $printtimescale(modulenume); 3 end

3) timescale 与`resetall成对使用

不要Load“projectname_run_msim_rtl_verilog.do”,否则会重新编译库。

3.5 SignalTap II

SignalTap II在加入Pre_synthesis Node之前,只需知道有哪些Node即可,并不需要做Fitter和Assembler。只需Start | Start Analysis and Elaboration即可,等加完Node后再做Start Compilation,这样可减少一次编译的时间。

post-fitting用于选择增量编译时,而pre-synthesis用于非增量编译时。

逮数据时只把Start触发沿设为rising edge。先Run逻辑分析仪,然后瞬间按下清零键,就可以逮到Start变高时的数据。

使用Signaltap II嵌入式逻辑分析仪时,注意采样深度不要设置过大,因为stp文件是要加入工程的,采样RAM占用了器件很大一部分memory bits。

研究生期间做项目所学到的一些经验,布布扣,bubuko.com

原文地址:http://www.cnblogs.com/clover-toeic/p/3765286.html