标签:

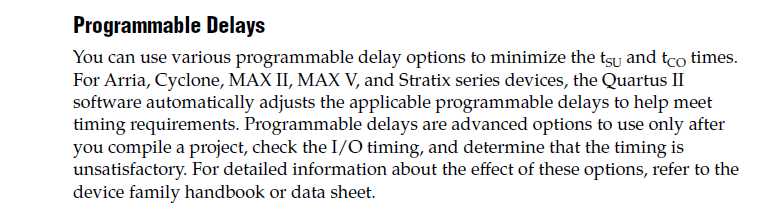

chip planner中一个io的结构如下图所示

其中左边是输出部分右边是输入部分,但是会注意到两个结构:1,寄存器,2,delay模块

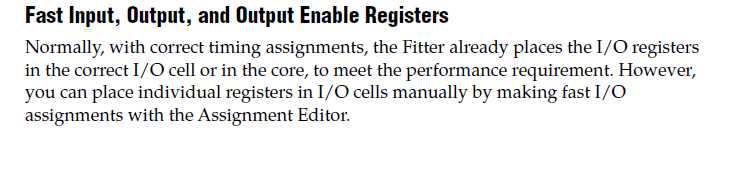

以下是我的推测:这两个结构是为了做时序优化时用的,在altera提供的时序优化文档中提到有快速输入输出寄存器在io cell里。

如果有正确的时序约束的话,quartus 软件是可以自动决定寄存器是放置到core里还是io cell里,但是也可以手动设置,方法是在assignment editor 里选择需要设置的管脚手动设置,如果是输入寄存器的话放到io cell 里是可以减少tsu的,如果是输出寄存器的话是可以减少tco的,

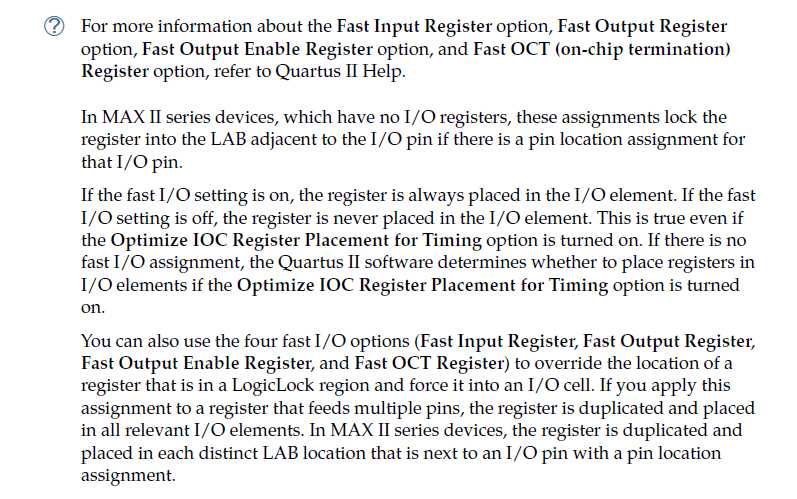

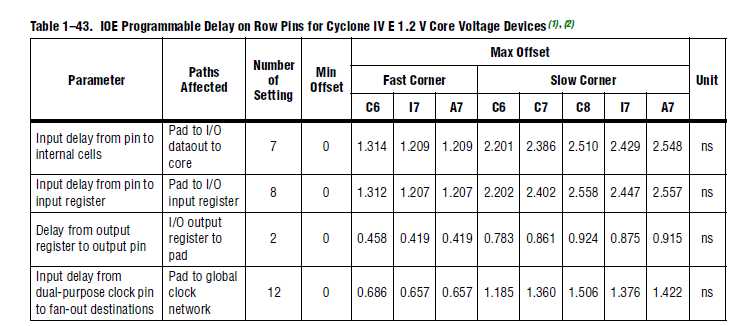

关于可编程delay,官方文档上有这样一段话

可见,官方是不推荐上去就调programmable delay 的,在编译完成之后产看时序不满足要求的情况下再修改programmable delay,

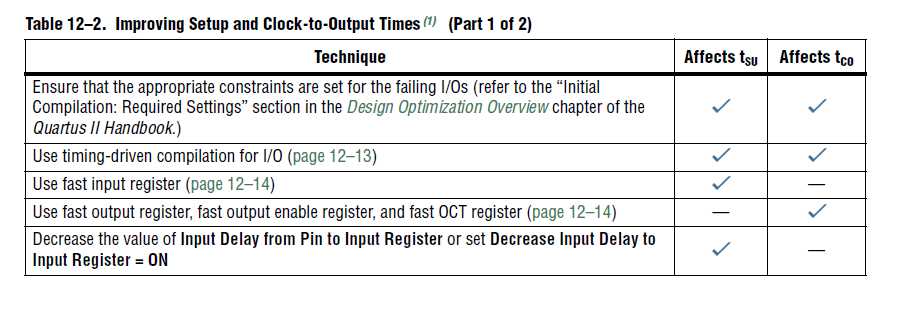

而我在device handbook中找到下面的表格

可以调整的delay就这么多。调整的方法也是在assignment editor 中调整。

标签:

原文地址:http://www.cnblogs.com/lianjiehere/p/4386762.html