标签:

1、Noise Margin

不管是TTL还是CMOS Logic Level,都会有门限。如,5V CMOS的VoutH > 4.4V, VoutL <0.33V;而它对应的输入电平VinH >3.5 , VinL <1.5V。所以,这里5V COMS的noise margin为VnH=4.4-3.5=0.9V。

为什么要有Noise Margin?因为信号在传输的时候会有噪音引入,同时,肯能会因为线路阻抗的不匹配而有发射信号在传输线上回荡。原本4.4V的高电平,加些乱七八糟的信号后,可能就连3.5V都没有了,如此便有了逻辑错误。

而且,越是低电平的逻辑,发生这种错误的可能越高。因为它没有足够大的Noise Margin,可能0.8V的反射(或Nois)对5V CMOS几乎没影响,但是对2.5 V CMOS就是致命打击。

2、loading&fan out

某个Output和其他好几个Input连接,这几个Input就成了该output的loading,及通常讲的负载。

每个output驱动Input或其他类型负载的能力是有限的, 这个极限称之为它的fan-out,多译做扇出。

①CMOS 类型的input,对驱动它的output而言,主要表现出它的容性;即,对output而言,可以等效这个负载为一个另一端接地的电容。而且,Level High到Level Low的过程,可以等效为output对对该电容充电;Level Low到Level High的过程,可以等效为该电容对output的放电。

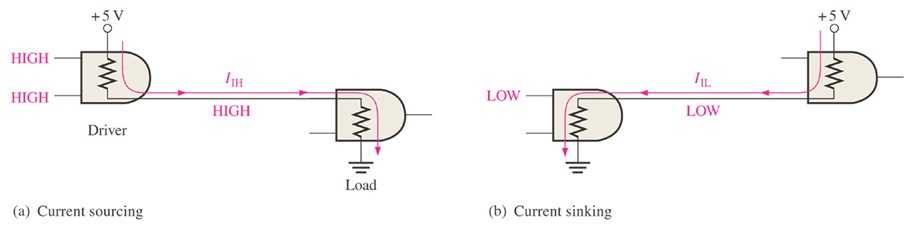

所以,描述一个逻辑门的时候,多会有IH和IL,这两个量一个表征高电平时能供应“流出”电流大小,另一个表征低电平时“流入”电流大小。

当负载超过output的驱动能力之后,因为要给多出“电容”充电的原因,传输的速率将大大降低。

②TTL 类型的I/O导通后事实上是通过电阻接VCC或者是GND,类似于下图:

所以TTL类型电路里面,输出低电平时的沉降电流(?current-sinking capability)是限制其驱动能力的最主要因素。

3、OD门和OC门

OD门全称是Open Drain Gates,是针对CMOS的栅极(Drain)而言的;OC门全称是Open Collector Gates是针对TTL的集电极(Collector)而言的。

使用OD门或者是OC门,都需要加上拉电阻到Vcc

4、悬空引脚的处理

TTL逻辑电平下,未使用的引脚一般会产生逻辑High;而未使用的CMOS管脚,最好是接地或者是接Vcc。

标签:

原文地址:http://www.cnblogs.com/pied/p/2308886.html