标签:

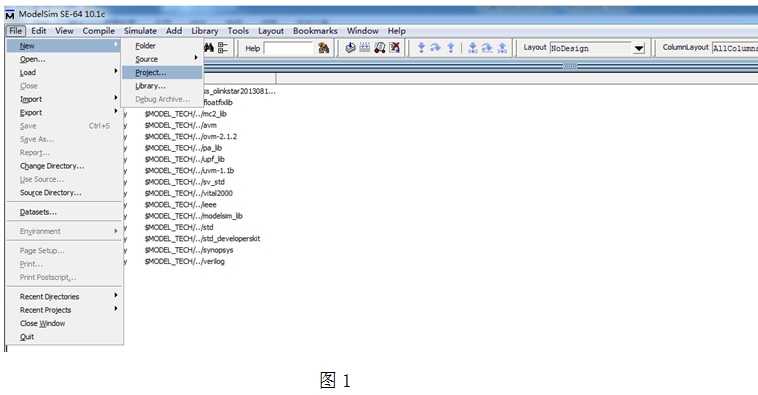

modelsim的工程文件为.mpf文件,可以理解为modulesim project file。首先,打开modelsim软件:如图1所示,从菜单项选择new->project

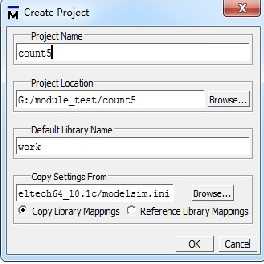

之后出现如图所示的对话框,project Name里需要填写项目名称,project Location是新建工程的路径,Default Library Name里一般默认库文件为work,这个一般不要修改,而copy settings from选项是工程的modelsim初始化文件从相应的库中拷贝出(即为modulsim.ini文件),这个选项一般也默认使用。这里,我们设计工程为一个计数器,名为count5。文件放置的位置,我们预先建立一个文件夹,名称也叫count5,如图2所示。

图2

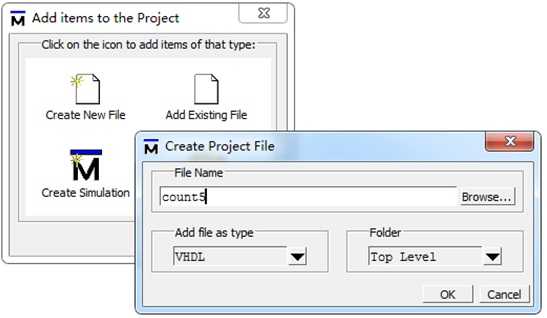

最后点击ok键。点击之后,出现对话框,Create New File表示新建一个文件,Add Existing File表示添加一个已经存在的文件,create Simulation表示新建一个仿真文件。这里,我们新建一个文件,如图3所示,file Name中输入新建的文件名,我们输入count5,Add file as type表示新建文件的类型,我们设计使用VHDL语言,Folder一般默认设置可。

图3

如果还需要继续新建文件名,可以继续点击。这里,我们先建立一个文件,以后如果需要还可以再加。这时,可以看到,出现了一个project选项页,选项页中出现一个文件,名为count5,类型为vhdl,即为我们刚刚所新建的文件,status一栏出现的问号表示此文件还没有被编译过。

双击count5文件,出现count5文件内容,当然目前它还是空的,编辑此文件,编写代码如下:

1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.std_logic_unsigned.all; 4 use ieee.std_logic_arith.all; 5 use std.textio.all; 6 use ieee.std_logic_textio.all; 7 8 entity count5 is 9 port( 10 rst_n : in std_logic; 11 clk : in std_logic; 12 cnt : out std_logic_vector(3 downto 0) 13 ); 14 end count5; 15 16 architecture behav of count5 is 17 signal cnt_in : std_logic_vector(3 downto 0); 18 file count_save :text open write_mode is "data/count_save.txt"; 19 file rf_data : text is in "data/rf.txt"; 20 begin 21 22 cnt<= cnt_in; 23 24 process(rst_n,clk) 25 variable data_line : line; 26 begin 27 if rst_n = ‘0‘ then 28 cnt_in <= (others => ‘0‘); 29 elsif clk‘event and clk = ‘1‘ then 30 cnt_in <= cnt_in + 1; 31 write(data_line,conv_integer(cnt_in)); 32 writeline(count_save,data_line); 33 end if; 34 end process; 35 36 end behav;

右击count5文件,在弹出的菜单中选择compile,表示要编译此文件。在compile 选项下,还有很多子选项,compile selected表示只编译选中的文件,compile all表示将工程中的所有文件都进行编译编译完后,文件的status变成一个对号,表示此文件编译正确。在modelsim软件的最下方,会有一个transcrip类似于控制台,可以输入命令行。

标签:

原文地址:http://www.cnblogs.com/fall-li/p/4392592.html