标签:

数码管的封装实验。显示使能信号置高才可以显示。对于小数点不用,故不显示。

数码管分为共阴数码管和共阳数码管,数码管不同,编码不同,下面是两种数码管显示0-F以及消隐的不同编码:

共阴数码管(高有效):

parameter seg_H_0 = 8‘h3f, seg_H_1 = 8‘h06, seg_H_2 = 8‘h5b, seg_H_3 = 8‘h4f, seg_H_4 = 8‘h66, seg_H_5 = 8‘h6d, seg_H_6 = 8‘h7d, seg_H_7 = 8‘h07, seg_H_8 = 8‘h7f, seg_H_9 = 8‘h67, seg_H_A = 8‘h77, seg_H_B = 8‘h7c, seg_H_C = 8‘h39, seg_H_D = 8‘h5e, seg_H_E = 8‘h79, seg_H_F = 8‘h71, seg_H_X = 8‘h00;

共阳数码管(低有效):

parameter seg_L_0 = 8‘hc0, seg_L_1 = 8‘hf9, seg_L_2 = 8‘ha4, seg_L_3 = 8‘hb0, seg_L_4 = 8‘h99, seg_L_5 = 8‘h92, seg_L_6 = 8‘h82, seg_L_7 = 8‘hf8, seg_L_8 = 8‘h80, seg_L_9 = 8‘h98, seg_L_A = 8‘h88, seg_L_B = 8‘h83, seg_L_C = 8‘hc6, seg_L_D = 8‘ha1, seg_L_E = 8‘h86, seg_L_F = 8‘h8e, seg_L_X = 8‘hff;

。

显示程序:

头文件

/********************************Copyright************************************** **----------------------------File information-------------------------- ** File name :seg_interface.v ** CreateDate :2015.04 ** Funtions :数码管封装,6位,数据为23位,4位在一个数码管上显示 ** Operate on :M5C06N3L114C7 ** Copyright :All rights reserved. ** Version :V1.0 **---------------------------Modify the file information---------------- ** Modified by : ** Modified data : ** Modify Content: *******************************************************************************/ module seg_interface( clk, rst_n, segdisplay_en, number_data, seg_data, seg_bit ); input clk; /* clk = 24M */ input rst_n; input [23:0] number_data; /* 输入的数据 */ input segdisplay_en; /* 数码管显示使能 */ output [7:0] seg_data; output [5:0] seg_bit; wire [7:0] seg_data; wire [5:0] seg_bit; wire [3:0] number_data_reg; smg_control U1( .clk(clk), .rst_n(rst_n), .segdisplay_en(segdisplay_en), .number_data(number_data), //in 23位输入数据 .seg_data_reg(number_data_reg), //数据的中间变量 out to U1 .seg_bit(seg_bit) //output 6 位数码管的位数 ); smg_encode U2( .number_data_reg(number_data_reg), //In 要显示的数据的中间变量 .seg_data(seg_data) ); endmodule

底层:

/********************************Copyright************************************** **----------------------------File information-------------------------- ** File name :smg_control.v ** CreateDate :2015.04 ** Funtions :数码管的位码控制和数据控制,状态机控制,1ms转移一位数码管 ** Operate on :M5C06N3L114C7 ** Copyright :All rights reserved. ** Version :V1.0 **---------------------------Modify the file information---------------- ** Modified by : ** Modified data : ** Modify Content: *******************************************************************************/ module smg_control( clk, rst_n, segdisplay_en, number_data, seg_data_reg, seg_bit ); input clk; input rst_n; input [23:0] number_data; //共使用6个数码管,每个4位数据,共24位 input segdisplay_en; output [3:0] seg_data_reg; output [5:0] seg_bit; wire [3:0] seg_data_reg; wire [5:0] seg_bit; parameter t1ms = 15‘d23999; /* reality */ // parameter t1ms = 15‘d3; /* just fo test */ reg [14:0] count1; always @(posedge clk or negedge rst_n) begin if(!rst_n) count1 <= ‘d0; else if(segdisplay_en) begin if(count1 == t1ms) count1 <= ‘d0; else count1 <= count1 + 1; end else count1 <= ‘d0; end //**************************************** reg [2:0] i; reg [3:0] rnumber; reg [5:0] rbit; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin i <= ‘d0; rnumber <= ‘d0; rbit <= 6‘b111111; /* 有消隐的作用 */ end else if(segdisplay_en) begin case(i) ‘d0: begin if(count1 == t1ms) i <= ‘d1; else begin rnumber <= number_data[23:20]; rbit <= 6‘b011111; end end ‘d1: begin if(count1 == t1ms) i <= ‘d2; else begin rnumber <= number_data[19:16]; rbit <= 6‘b101111; end end ‘d2: begin if(count1 == t1ms) i <= ‘d3; else begin rnumber <= number_data[15:12]; rbit <= 6‘b110111; end end ‘d3: begin if(count1 == t1ms) i <= ‘d4; else begin rnumber <= number_data[11:8]; rbit <= 6‘b111011; end end ‘d4: begin if(count1 == t1ms) i <= ‘d5; else begin rnumber <= number_data[7:4]; rbit <= 6‘b111101; end end ‘d5: begin if(count1 == t1ms) i <= ‘d0; else begin rnumber <= number_data[3:0]; rbit <= 6‘b111110; end end default : i <= ‘d0; endcase end else begin i <= ‘d0; rnumber <= ‘d0; rbit <= 6‘b111111; /* 有消隐的作用 */ end end assign seg_data_reg = rnumber; assign seg_bit = rbit; endmodule

/********************************Copyright************************************** **----------------------------File information-------------------------- ** File name :smg_encode.v ** CreateDate :2015.04 ** Funtions :数码管的编码文件,输入4位,输出8位 ** Operate on :M5C06N3L114C7 ** Copyright :All rights reserved. ** Version :V1.0 **---------------------------Modify the file information---------------- ** Modified by : ** Modified data : ** Modify Content: *******************************************************************************/ module smg_encode ( number_data_reg, seg_data ); input [3:0] number_data_reg; output [7:0] seg_data; wire [7:0] seg_data; //parameter seg_0 = 8‘b1100_0000, seg_1 = 8‘b1111_1001, seg_2 = 8‘b1010_0100, // seg_3 = 8‘b1011_0000, seg_4 = 8‘b1001_1001, seg_5 = 8‘b1001_0010, // seg_6 = 8‘b1000_0010, seg_7 = 8‘b1111_1000, seg_8 = 8‘b1000_0000, // seg_9 = 8‘b1001_0000; // ---- // | | // | | // ---- // | | // | | // ---- 。 parameter seg_H_0 = 8‘h3f, seg_H_1 = 8‘h06, seg_H_2 = 8‘h5b, seg_H_3 = 8‘h4f, seg_H_4 = 8‘h66, seg_H_5 = 8‘h6d, seg_H_6 = 8‘h7d, seg_H_7 = 8‘h07, seg_H_8 = 8‘h7f, seg_H_9 = 8‘h67, seg_H_A = 8‘h77, seg_H_B = 8‘h7c, seg_H_C = 8‘h39, seg_H_D = 8‘h5e, seg_H_E = 8‘h79, seg_H_F = 8‘h71, seg_H_X = 8‘h00; /* parameter seg_L_0 = 8‘hc0, seg_L_1 = 8‘hf9, seg_L_2 = 8‘ha4, seg_L_3 = 8‘hb0, seg_L_4 = 8‘h99, seg_L_5 = 8‘h92, seg_L_6 = 8‘h82, seg_L_7 = 8‘hf8, seg_L_8 = 8‘h80, seg_L_9 = 8‘h98, seg_L_A = 8‘h88, seg_L_B = 8‘h83, seg_L_C = 8‘hc6, seg_L_D = 8‘ha1, seg_L_E = 8‘h86, seg_L_F = 8‘h8e, seg_L_X = 8‘hff; */ //********************************************************* reg [7:0] rsmg; always @(*) begin case(number_data_reg) 4‘h0: rsmg <= seg_H_0; 4‘h1: rsmg <= seg_H_1; 4‘h2: rsmg <= seg_H_2; 4‘h3: rsmg <= seg_H_3; 4‘h4: rsmg <= seg_H_4; 4‘h5: rsmg <= seg_H_5; 4‘h6: rsmg <= seg_H_6; 4‘h7: rsmg <= seg_H_7; 4‘h8: rsmg <= seg_H_8; 4‘h9: rsmg <= seg_H_9; 4‘ha: rsmg <= seg_H_A; 4‘hb: rsmg <= seg_H_B; 4‘hc: rsmg <= seg_H_C; 4‘hd: rsmg <= seg_H_D; 4‘he: rsmg <= seg_H_E; 4‘hf: rsmg <= seg_H_F; default : rsmg <= seg_H_X; endcase end assign seg_data= rsmg; endmodule

测试文件:

/********************************Copyright************************************** **----------------------------File information-------------------------- ** File name :seg_tb.v ** CreateDate :2015.04 ** Funtions : 数码管的测试文件 ** Operate on :M5C06N3L114C7 ** Copyright :All rights reserved. ** Version :V1.0 **---------------------------Modify the file information---------------- ** Modified by : ** Modified data : ** Modify Content: *******************************************************************************/ `timescale 1 ns/1 ns module seg_tb; reg clk; /* clk = 24M */ reg rst_n; reg [23:0] number_data; /* 输入的数据 */ reg segdisplay_en; wire [7:0] seg_data; wire [5:0] seg_bit; seg_interface seg_interface1( .clk, .rst_n, .number_data, .segdisplay_en(segdisplay_en), .seg_data, .seg_bit ); parameter tck = 24; parameter t = 1000/tck; always #(t/2) clk = ~clk; initial begin clk = 0; rst_n = 0; number_data = 0; segdisplay_en = 0; #(20*t) rst_n = 1; #(20*t) segdisplay_en = 1; number_data = 24‘h123456; #(100*t) number_data = 24‘h789abc; end endmodule

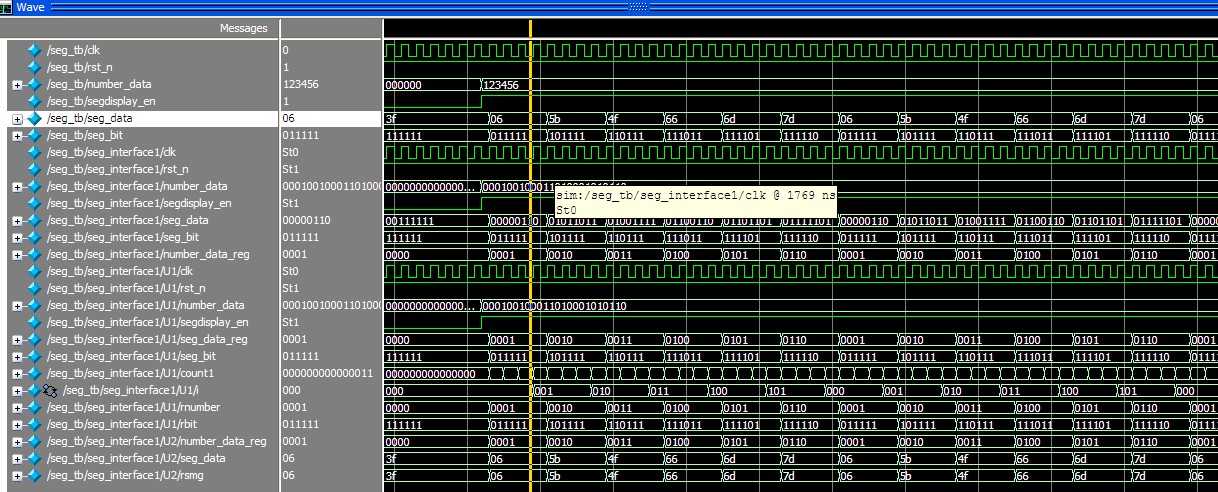

仿真图:

标签:

原文地址:http://www.cnblogs.com/fhyfhy/p/4421606.html