标签:

cb说完美是没有极限的,对此我表示赞同,自从用了cb的板子,玩开cmos,fpga,sdram,vga等。

不断涌现的是,双端口sdram,四端口sdram,各式各样的封装,但是大同小异,但总是有些不同,对于初学的我,感觉还是挺费事,玩转各种例程发现,cb的sdram驱动程序很强大但并不完美,其中对sdram有挑选作用,如hy57v641620ftp-7很ok的使用,换成hy57v641620ftp-6就有问题,但是使用其他版本程序测试,这两个ic均ok。

这个问题一度困扰过cb良久,最终cb偶然发现,将突发长度从256改为128,就能好好的解决,自此,解决了问题(详情参阅cb博客)

但是这样可能并不完美,需要深究其根本,就得仔细阅读内部代码,仔细推敲,本人水平有限,所以只能一步一个脚印。

现将兼容和不兼容的程序统一接口,使得程序更好移植,逻辑更加清晰。

ps:cb的接口已经做得很棒,只是我不太习惯,以下移植接口,按照我的思维理解方式修改。

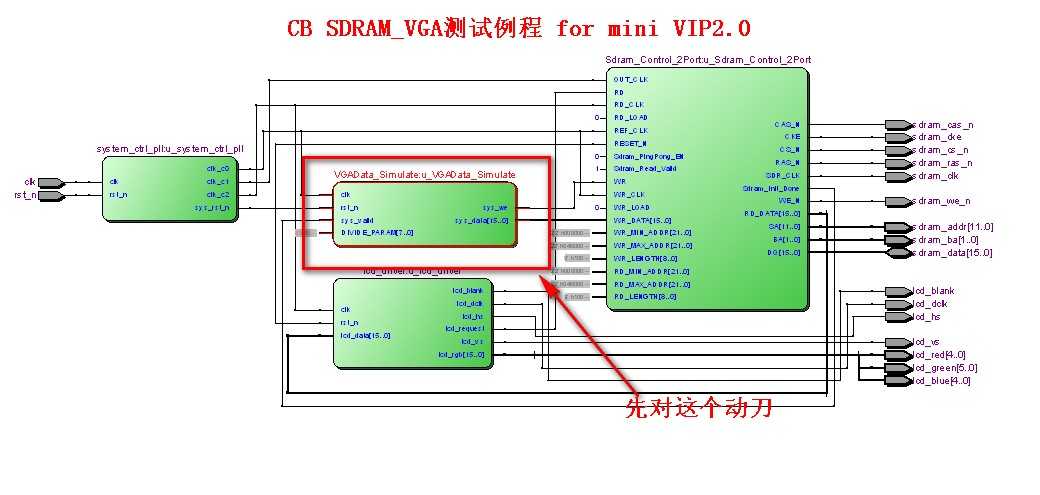

先看看cb现有的接口

改造中

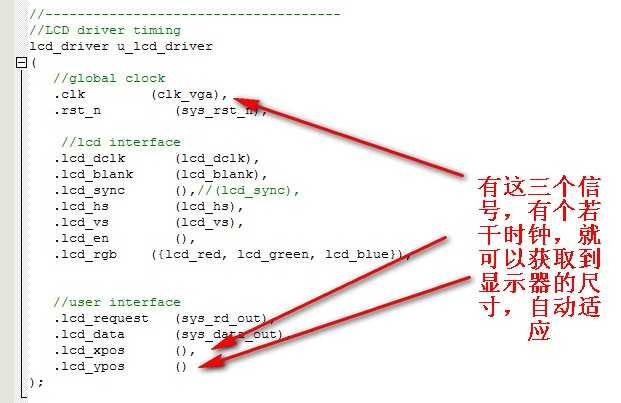

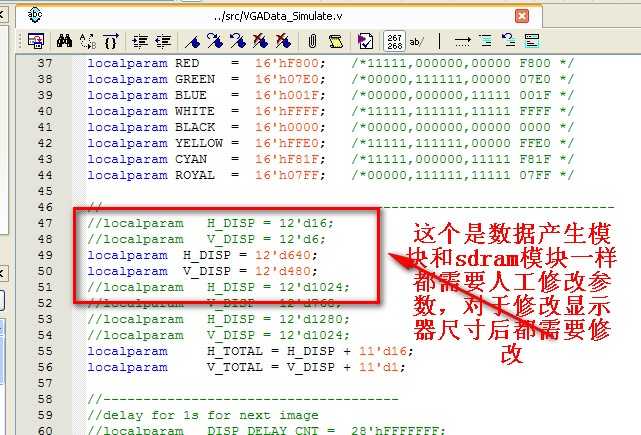

1、

module LCDData_Simulate

(

input clk, //globan clock

input rst_n, //Global reset

input sys_vaild, //the device is ready

input[7:0] DIVIDE_PARAM, //0-255

input[11:0] X_size, // 增加x尺寸大小输入,

input[11:0] Y_size, // 增加y尺寸大小输入,

//sys 2 sdram control

output disp_valid, // 增加显示有效信号输出,告知设备,目前输出像素有效,类似显示的帧同步信号

output reg [15:0] sys_data,

output sys_we

);

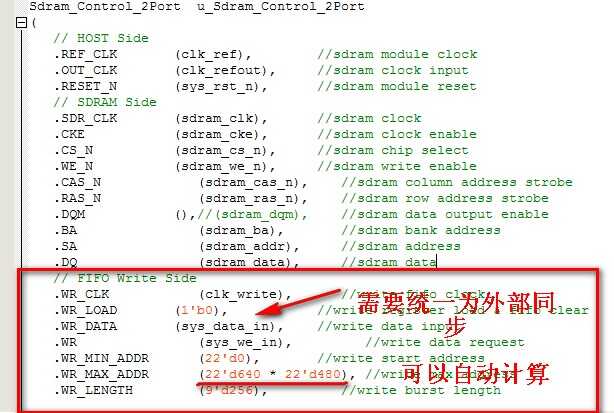

2、SDRAM_VGA_Display_Test

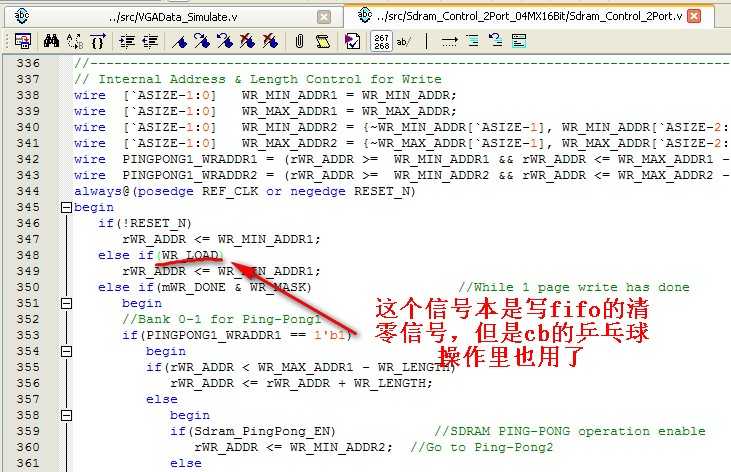

增加 WR_LOAD信号,根据数据产生模块的帧有效的信号,产生一个脉冲,高电平脉冲,在帧同步信号结束时产生,用于清除fifo

wire WR_LOAD;

reg sys_disp_valid_r1;

reg sys_disp_valid_r2;

always@(posedge clk_ref)

begin

sys_disp_valid_r1<=sys_disp_valid;

sys_disp_valid_r2<=sys_disp_valid_r1;

end

assign WR_LOAD=sys_disp_valid_r1&(!sys_disp_valid_r1);

3、SDRAM_VGA_Display_Test

// FIFO Write Side

.WR_CLK (clk_write), //write fifo clock

.WR_LOAD (WR_LOAD), //使用此信号

.WR_DATA (sys_data_in), //write data input

.WR (sys_we_in), //write data request

.WR_MIN_ADDR (22‘d0), //write start address

.WR_MAX_ADDR (`H_DISP * `V_DISP *22‘d1), //write max address

.WR_LENGTH (9‘d256), //write burst length

就此,第一步兼容已经完成,此目的已经达到数据产生模块任意间隔产生数据,保证同步,下一再实现显示器尺寸自动匹配功能。

标签:

原文地址:http://www.cnblogs.com/ccjt/p/4423744.html