标签:

1 Scenarios

There are two scenarios that are possible when passing signals across CDC boundaries:

1st scenario: sometimes it is not necessary to sample every value, but it is important that the sampled values are accurate.

One example is the set of gray code counters used in a standard asynchronous FIFO design. In a properly designed asynchronous FIFO model, synchronized gray code counters do not need to capture every legal value from the opposite clock domain, but it is critical that sampled values be accurate to recognize when full and empty conditions have occurred.

2nd scenario: a CDC signal must be properly recognized or recognized and acknowledged before a change is permitted on the CDC signal.

In both of these scenarios, the CDC signals will require some form of synchronization into the receiving clock domain.

2 Receiving clock domain

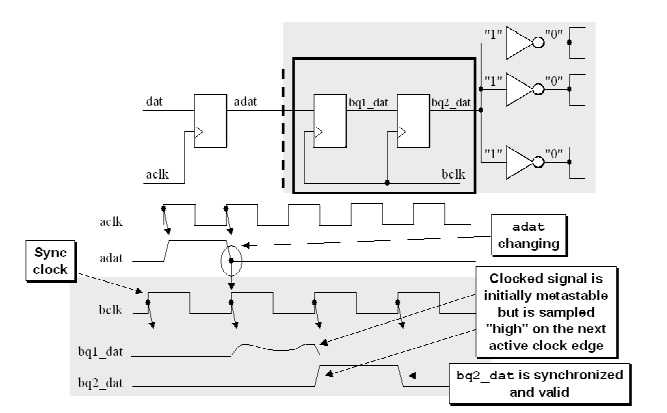

1) Two flip-flop synchronizer

For most synchronization applications, the two flip-flop synchronizer is sufficient to remove all likely metastability.

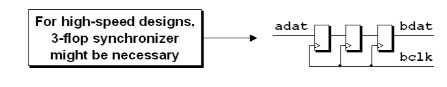

2) Three flip-flop synchronizer

For some very high speed designs, a third flop is added to increase the MTBF to a satisfactory duration of time.

3 Sending clock domain

Registering signals in the sending clock domain should generally be rquired.

4 Three edge

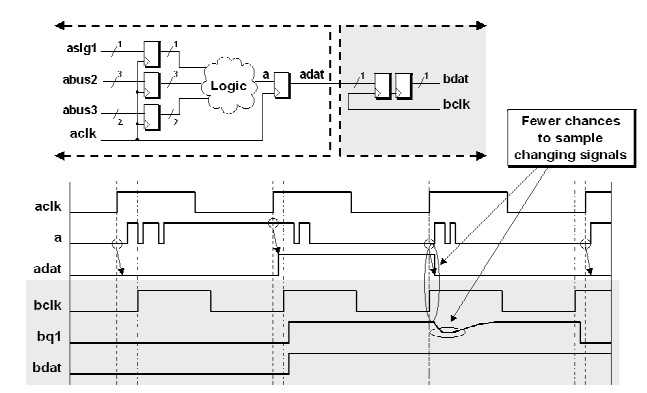

Recognizing that sampling slower signals into faster clock domains causes fewer potential problems than sampling faster signals into slower clock domains, a designer might take advantage of this fact by using simple two flip-flop synchronizers to pass single CDC signals between clock domains.

When passing one CDC signal between clock domains through a two-flip-flop synchronizer, the CDC signal must be wider than 1-1/2 times the cycle width of the receiving domain clock period. (Input values must be stable for three destination clock edges)

For exceptionally long source and destination clock frequencies, this requirement could probably be safely relaxed to 1-1/4 times the cycle time of the receiving clock domain or less, but the "three edge" guideline is the safest initial design condition, and is easier to prove through the use of SystemVerilog assertions than to dynamically measure a fractional width of a CDC signal during simulation.

标签:

原文地址:http://www.cnblogs.com/mengdie/p/4488880.html