标签:

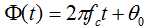

从两式可以看出,正弦信号是关于相位的一个周期函数,下图更加直观的描述相位与幅度的关系,16个相位与16个幅度值相对应,即每一个相位值对应一个幅度值,比如1100对应的相位为3π/2,对应的幅度值为-1.

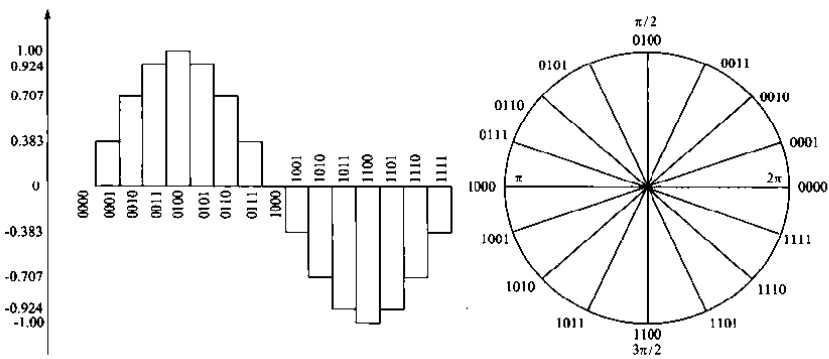

相位和幅值的一一对应关系就好比存储器中地址和存储内容的关系,如果把一个周期内每个相位对应的幅度值存入存储器当中,那么对于任意频率的正弦信号,在任意时刻,只要已知相位Φ(t),也就知道地址,就可通过查表得到s(t)。下图是DDS的基本结构框图:

频率分辨率,即频率的变化间隔

module DDS (sys_clk,sys_rst_n,freq_word,phase_word,wave_out);input sys_clk ; //系统工作时钟input sys_rst_n ; //复位,低有效input [31:0] freq_word ; //频率控制字,控制输出波形频率input [11:0] phase_word ; //相位控制字,控制初始相位output[9:0] wave_out ; //输出波形,位宽10bitreg [31:0] freq_word_reg ;reg [11:0] phase_word_reg ;reg [31:0] phase_adder ; //相位累加器reg [9:0] rom_address ; //存储深度2^10always @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1‘b0) beginfreq_word_reg <= 32‘h0000;endelsefreq_word_reg <= freq_word;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1‘b0) beginphase_word_reg <= 12‘h0000;endelsephase_word_reg <= phase_word;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1‘b0) beginphase_adder <= 32‘h0000;endelsephase_adder <= phase_adder + freq_word_reg; //对频率控制字进行累加endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1‘b0) beginrom_address <= 32‘h0000;endelserom_address <= phase_adder[31:20] + phase_word_reg;endsin_rom DDS_ROM_U0 (.address (rom_address) ,.clock (sys_clk) ,.q (wave_out));endmodule

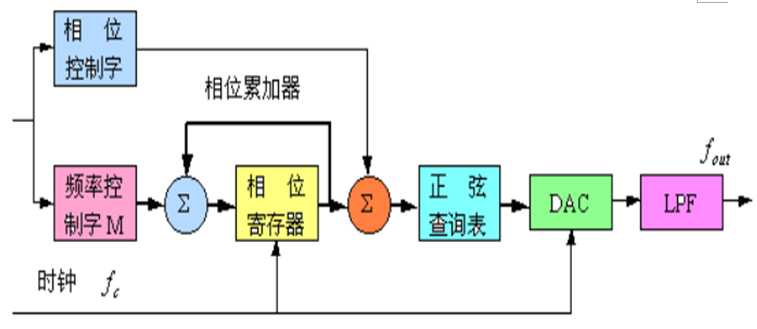

`timescale 1 ns/ 1 nsmodule DDS_tb();reg [31:0] freq_word ;reg [11:0] phase_word ;reg sys_clk ;reg sys_rst_n ;wire [9:0] wave_out ;DDS i1 (.freq_word(freq_word),.phase_word(phase_word),.sys_clk(sys_clk),.sys_rst_n(sys_rst_n),.wave_out(wave_out));initialbeginsys_clk = 0;sys_rst_n = 0;freq_word = 0;phase_word = 0;#2000;sys_rst_n = 1;freq_word = 32‘d1024; //25Mphase_word = 32‘d0; //相位0度#200000000;freq_word = 32‘d2048; //50Mphase_word = 32‘d512; //相位90度#200000000;$stop;endalways sys_clk = #20 ~sys_clk; //系统时钟25Mendmodule

标签:

原文地址:http://www.cnblogs.com/yfwblog/p/4515375.html