标签:

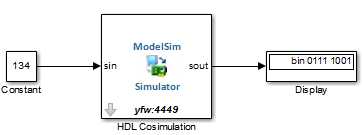

当使用硬件描述语言(HDL)完成电路设计时,往往需要编写Testbench对所设计的电路进行仿真验证,测试设计电路的功能是否与预期的目标相符。而编写Testbench难度之大,这时可以借助交互式图形化环境Simulink来产生模拟激励,并且可以观察测试模块的输出响应。

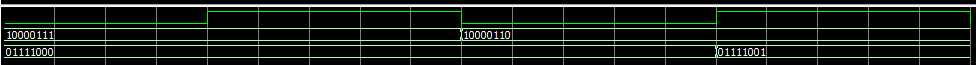

module inverter(clk,sin,sout);input clk ;input [7:0] sin ;output [7:0] sout ;reg [7:0] sout;always@(posedge clk)sout <= ~ sin;endmodule

标签:

原文地址:http://www.cnblogs.com/yfwblog/p/4518100.html