标签:

WHEN (simple and selected)

It is one of the fundamental concurrent statements (along with operators and GENERATE).

It appears in two forms: WHEN / ELSE (simple WHEN) and WITH / SELECT / WHEN (selected WHEN).

1) WHEN / ELSE:

assignment WHEN condition ELSE assignment WHEN condition ELSE ...;

2) WITH / SELECT / WHEN:

WITH identifier SELECT assignment WHEN value, assignment WHEN value,

...;

Example

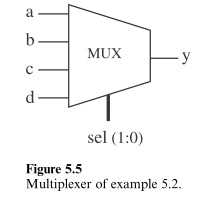

Solution 1

1 ------- Solution 1: with WHEN/ELSE -------- 2 LIBRARY ieee; 3 USE ieee.std_logic_1164.all; 4 ------------------------------------------- 5 ENTITY mux IS 6 PORT ( a, b, c, d: IN STD_LOGIC; 7 sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0); 8 y: OUT STD_LOGIC); 9 END mux; 10 ------------------------------------------- 11 ARCHITECTURE mux1 OF mux IS 12 BEGIN 13 y <= a WHEN sel="00" ELSE 14 b WHEN sel="01" ELSE 15 c WHEN sel="10" ELSE 16 d; 17 END mux1; 18 -------------------------------------------

Solution 2

1 --- Solution 2: with WITH/SELECT/WHEN ----- 2 LIBRARY ieee; 3 USE ieee.std_logic_1164.all; 4 ------------------------------------------- 5 ENTITY mux IS 6 PORT ( a, b, c, d: IN STD_LOGIC; 7 sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0); 8 y: OUT STD_LOGIC); 9 END mux; 10 ------------------------------------------- 11 ARCHITECTURE mux2 OF mux IS 12 BEGIN 13 WITH sel SELECT 14 y <= a WHEN "00", -- notice "," instead of ";" 15 b WHEN "01", 16 c WHEN "10", 17 d WHEN OTHERS; -- cannot be "d WHEN "11" " 18 END mux2; 19 --------------------------------------------

标签:

原文地址:http://www.cnblogs.com/mengdie/p/4518340.html