标签:

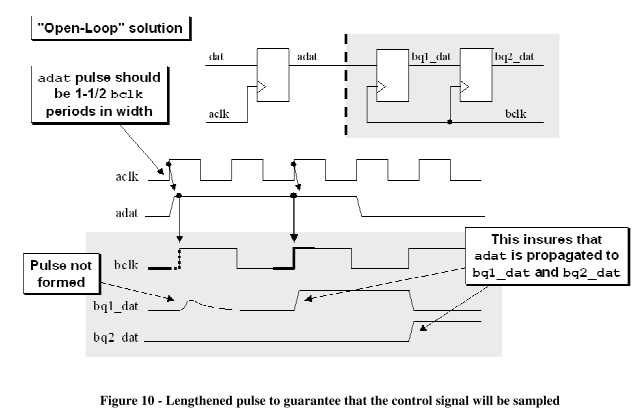

1 Open-loop solution

One potential solution is to assert CDC signals for a period of time that exceeds the cycle time of the sampling clock as shown in Figure. As discussed in fast->slow (1), the minimum pulse width is 1.5X the period of the receiving clock frequency. The assumption is that the CDC signal will be sampled at least once and possibly twice by the receiver clock.

Advantage: it is the fastest way to pass signals across CDC boundaries that does not require acknowledgement of the received signal.

Disadvantage: the largest potential problem is that another engineer might mistake the solution for a general purpose solution, or the design requirements might change and an engineer might fail to re-analyze the original open loop solution. This problem can be minimized by adding a SystemVerilog Assertion to the model to detect if the input pulse ever fails to exceed the "three edges" design requirement.

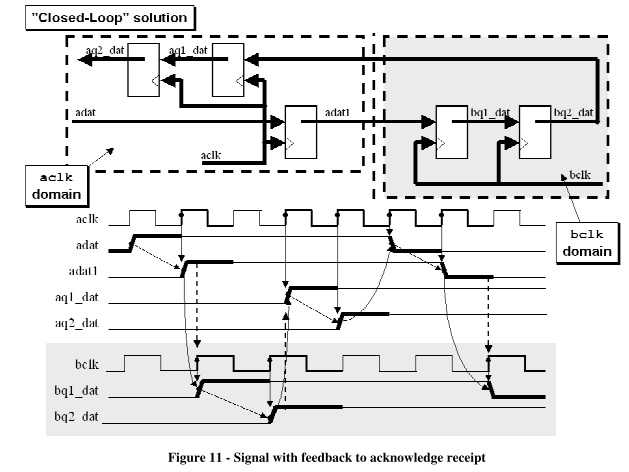

2 Closed-loop solution

A second potential solution is to send an enabling control signal, synchronize it into the new clock domain and then pass the synchronized signal back through another synchronizer to the sending clock domain as an acknowledge signal.

Advantage: synchronizing a feedback signal is very safe to acknowledge that the first control signal was recognized and sampled into the new clock domain.

Disadvantage: there is potentially considerable delay associated with synchronizing control signals in both directions before allowing the control signal to change.

标签:

原文地址:http://www.cnblogs.com/mengdie/p/4520743.html