标签:

Recognizing that sampling slower signals into faster clock domains causes fewer potential problems than sampling faster signals into slower clock domains, a designer might take advantage of this fact by using simple two flip-flop synchronizers to pass single CDC signals between clock domains.

1 "three edge" requirement

When passing one CDC signal between clock domains through a two-flip-flop synchronizer, the CDC signal must be wider than 1-1/2 times the cycle width of the receiving domain clock period. (Input values must be stable for three destination clock edges)

For exceptionally long source and destination clock frequencies, this requirement could probably be safely relaxed to 1-1/4 times the cycle time of the receiving clock domain or less, but the "three edge" guideline is the safest initial design condition, and is easier to prove through the use of SystemVerilog assertions than to dynamically measure a fractional width of a CDC signal during simulation.

2 Problem

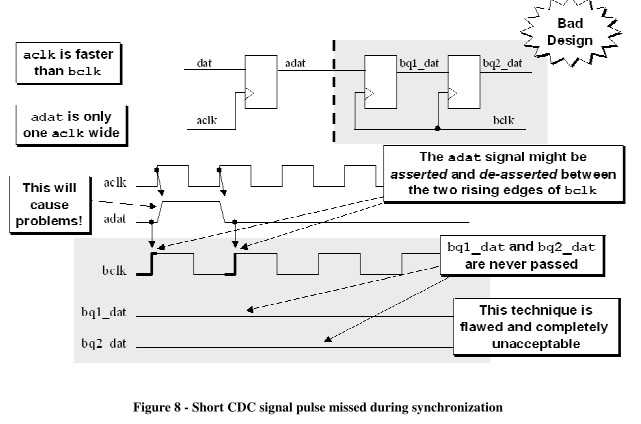

1) CDC pulse ≈ one fast-clock cycle < one slow-clock cycle

If the CDC signal is only pulsed for one fast-clock cycle, the CDC signal could go high and low between the rising edges of a slower clock and not be captured into the slower clock domain as shown in Figure.

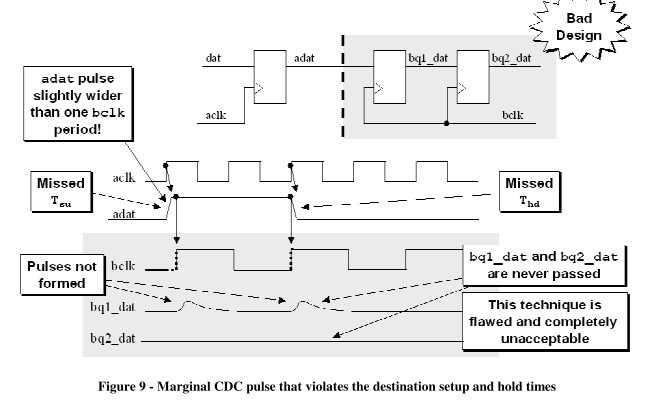

2) CDC pulse >≈ one slow-clock cycle >> one fast-clock cycle

Under most conditions, the signal will be sampled and passed, but there is the small chance that the CDC pulse will change too close to the two rising clock edges of the receiving clock domain and thereby violate the setup time on the first clock edge and violate the hold time of the second clock edge and not form the anticipated pulse. This possible failure is shown in Figure.

标签:

原文地址:http://www.cnblogs.com/mengdie/p/4520348.html