标签:

Static Timing Analysis is one of the many techniques available to verify the timing of a digital design. An alternate approach used to verify the timing is the timing simulation which can verify the functionality as well as the timing of the design. The term timing analysis is used to refer to either of these two methods - static timing analysis, or the timing simulation.

1 Propagation delay

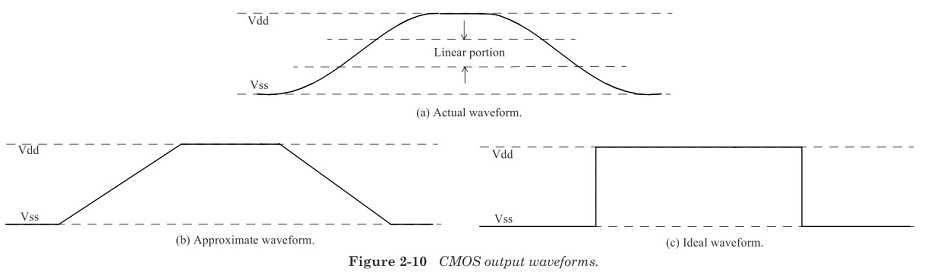

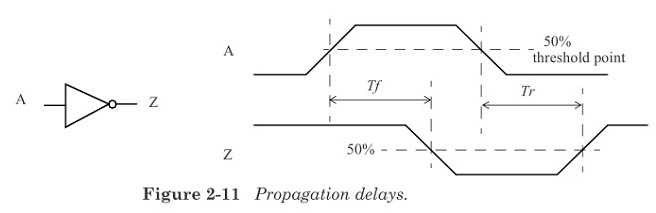

Consider a CMOS inverter cell and its input and output waveforms. The propagation delay of the cell is defined with respect to some measurement points on the switching waveforms.

Consider the example inverter cell and the waveforms at its pins shown following. The propagation delays are represented as:

- Output fall delay (Tf)

- Output rise delay (Tr)

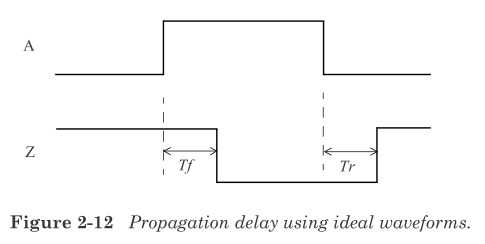

If we were looking at ideal waveforms, propagation delay would simply be the delay between the two edges.

1 # Threshold point of an input falling edge: 2 input_threshold_pct_fall : 50.0; 3 # Threshold point of an input rising edge: 4 input_threshold_pct_rise : 50.0; 5 # Threshold point of an output falling edge: 6 output_threshold_pct_fall : 50.0; 7 # Threshold point of an output rising edge: 8 output_threshold_pct_rise : 50.0;

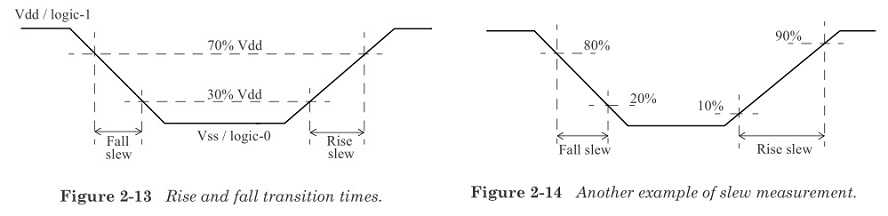

2 Slew of a Waveform

A slew rate is defined as a rate of change. In static timing analysis, the rising or falling waveforms are measured in terms of whether the transition is slow or fast. The slew is typically measured in terms of the transition time.

1 # Falling edge thresholds: 2 slew_lower_threshold_pct_fall : 30.0; 3 slew_upper_threshold_pct_fall : 70.0; 4 # Rising edge thresholds: 5 slew_lower_threshold_pct_rise : 30.0; 6 slew_upper_threshold_pct_rise : 70.0;

1 # Falling edge thresholds: 2 slew_lower_threshold_pct_fall : 20.0; 3 slew_upper_threshold_pct_fall : 80.0; 4 # Rising edge thresholds: 5 slew_lower_threshold_pct_rise : 10.0; 6 slew_upper_threshold_pct_rise : 90.0;

标签:

原文地址:http://www.cnblogs.com/mengdie/p/4603253.html