标签:

我想大家都知道,队列是计算机系统中一种比较基本的数据结构。作为队列中的一种,先进先出的FIFO是一种比较常用的存储器单元。FIFO通常有读允许端口、写允许端口、数据输入端口、数据输出端口、FIFO状态端口等信号端口。其中,FIFO状态端口输出当前FIFO的状态——满、未满或空。

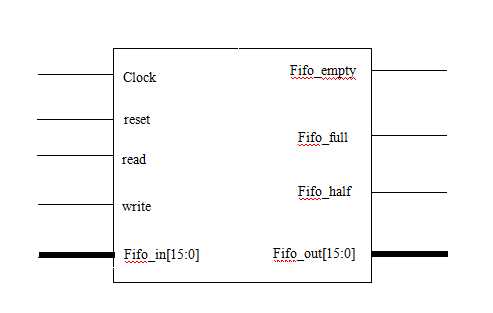

16*16位FIFO的功能框图如下。其中,clock为系统时钟信号输入,reset为系统复位信号,read为读数据信号允许信号,write为写入FIFO允许信号,fifo_in[15:0]为数据输入,fifo_out[15:0]为数据输出,fifo_empty为指示FIFO当前是空的,这种情况下,只能对FIFO进行写入数据操作;fifo_full指示当前FIFO是满的,这种情况下,当然只能对FIFO进行读数据操作,是不能写入数据的;fifo_half指示当前FIFO队列中没空也没满,这种情况下,既可以对FIFO进行写入数据操作,也能进行读数据操作。

16*16位FIFO读写数据操作的Verilog HDL的代码整理如下。

module FIFO_16_16(

clock,reset,

read,write,fifo_in,fifo_out,

fifo_empty,fifo_full,fifo_half);

input clock,reset,read,write;

input [15:0] fifo_in;

output [15:0] fifo_out;

output fifo_empty,fifo_full,fifo_half;

reg [15:0] fifo_out;

reg [3:0] read_ptr,write_ptr,counter;

reg [15:0] ram [15:0];

wire fifo_empty,fifo_full,fifo_half;

always @(posedge clock)

if(reset)

begin

read_ptr=0;

write_ptr=0;

counter=0;

fifo_out=0;

end

else

case({read,write})

2‘b00: counter=counter;

2‘b01: begin

ram[write_ptr]=fifo_in;

counter=counter+1;

write_ptr=(write_ptr==15)?0:write_ptr+1;

end

2‘b10: begin

fifo_out=ram[read_ptr];

counter=counter-1;

read_ptr=(read_ptr==15)?0:read_ptr+1;

end

2‘b11: begin

if(counter==0)

fifo_out=fifo_in;

else

begin

ram[write_ptr]=fifo_in;

fifo_out=ram[read_ptr];

write_ptr=(write_ptr==15)?0:write_ptr+1;

read_ptr=(read_ptr==15)?0:read_ptr+1;

end

end

endcase

assign fifo_empty=(counter==0);

assign fifo_full=(counter==15);

assign fifo_half=(counter==8);

endmodule

标签:

原文地址:http://www.cnblogs.com/w1341787781/p/4604120.html