标签:

此例程为STM324x9I_EVAL:DCMI_CaptureMode,使用的stm32f4xx_hal_driver,

At each camera line event, the line is converted to ARGB8888 pixel format

and transferred to LCD_FRAME_BUFFER using DMA2D.

这里仅记录例程中DMA2D这段,Camera RGB565格式 LCD RGB888

1 /** 2 * @brief Converts a line to an ARGB8888 pixel format. 3 * @param pSrc: Pointer to source buffer 4 * @param pDst: Output color 5 * @param xSize: Buffer width 6 * @param ColorMode: Input color mode 7 * @retval None 8 */ 9 static void LCD_LL_ConvertLineToARGB8888(void *pSrc, void *pDst) 10 { 11 /* Enable DMA2D clock */ 12 __HAL_RCC_DMA2D_CLK_ENABLE(); 13 14 /* Configure the DMA2D Mode, Color Mode and output offset */ 15 hdma2d_eval.Init.Mode = DMA2D_M2M_PFC; 16 hdma2d_eval.Init.ColorMode = DMA2D_ARGB8888; 17 hdma2d_eval.Init.OutputOffset = 0; 18 19 /* Foreground Configuration */ 20 hdma2d_eval.LayerCfg[1].AlphaMode = DMA2D_NO_MODIF_ALPHA; 21 hdma2d_eval.LayerCfg[1].InputAlpha = 0xFF; 22 hdma2d_eval.LayerCfg[1].InputColorMode = CM_RGB565; 23 hdma2d_eval.LayerCfg[1].InputOffset = 0; 24 25 hdma2d_eval.Instance = DMA2D; 26 27 /* DMA2D Initialization */ 28 if(HAL_DMA2D_Init(&hdma2d_eval) == HAL_OK) 29 { 30 if(HAL_DMA2D_ConfigLayer(&hdma2d_eval, 1) == HAL_OK) 31 { 32 if (HAL_DMA2D_Start(&hdma2d_eval, (uint32_t)pSrc, (uint32_t)pDst, BSP_LCD_GetXSize(), 1) == HAL_OK) 33 { 34 /* Polling For DMA transfer */ 35 HAL_DMA2D_PollForTransfer(&hdma2d_eval, 10); 36 } 37 } 38 } 39 else 40 { 41 /* FatFs Initialization Error */ 42 Error_Handler(); 43 } 44 }

分析初始化中代码:static DMA2D_HandleTypeDef hdma2d_eval;

1 typedef struct __DMA2D_HandleTypeDef 2 { 3 DMA2D_TypeDef *Instance; /*!< DMA2D Register base address */ 4 5 DMA2D_InitTypeDef Init; /*!< DMA2D communication parameters */ 6 7 void (* XferCpltCallback)(struct __DMA2D_HandleTypeDef * hdma2d); /*!< DMA2D transfer complete callback */ 8 9 void (* XferErrorCallback)(struct __DMA2D_HandleTypeDef * hdma2d); /*!< DMA2D transfer error callback */ 10 11 DMA2D_LayerCfgTypeDef LayerCfg[MAX_DMA2D_LAYER]; /*!< DMA2D Layers parameters */ 12 13 HAL_LockTypeDef Lock; /*!< DMA2D Lock */ 14 15 __IO HAL_DMA2D_StateTypeDef State; /*!< DMA2D transfer state */ 16 17 __IO uint32_t ErrorCode; /*!< DMA2D Error code */ 18 } DMA2D_HandleTypeDef;

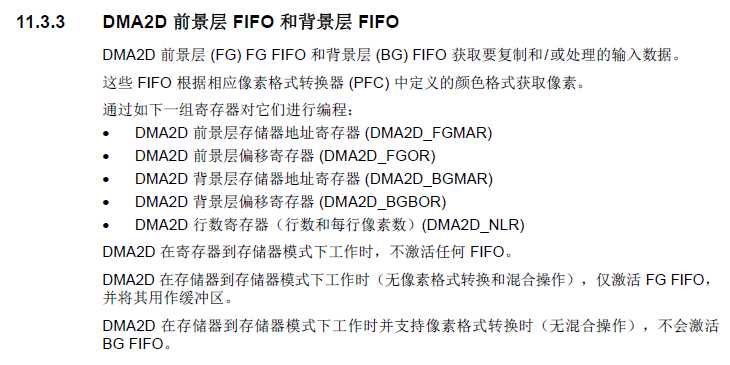

1 typedef struct 2 { 3 __IO uint32_t CR; /*!< DMA2D Control Register, Address offset: 0x00 */ 4 __IO uint32_t ISR; /*!< DMA2D Interrupt Status Register, Address offset: 0x04 */ 5 __IO uint32_t IFCR; /*!< DMA2D Interrupt Flag Clear Register, Address offset: 0x08 */ 6 __IO uint32_t FGMAR; /*!< DMA2D Foreground Memory Address Register, Address offset: 0x0C */ 7 __IO uint32_t FGOR; /*!< DMA2D Foreground Offset Register, Address offset: 0x10 */ 8 __IO uint32_t BGMAR; /*!< DMA2D Background Memory Address Register, Address offset: 0x14 */ 9 __IO uint32_t BGOR; /*!< DMA2D Background Offset Register, Address offset: 0x18 */ 10 __IO uint32_t FGPFCCR; /*!< DMA2D Foreground PFC Control Register, Address offset: 0x1C */ 11 __IO uint32_t FGCOLR; /*!< DMA2D Foreground Color Register, Address offset: 0x20 */ 12 __IO uint32_t BGPFCCR; /*!< DMA2D Background PFC Control Register, Address offset: 0x24 */ 13 __IO uint32_t BGCOLR; /*!< DMA2D Background Color Register, Address offset: 0x28 */ 14 __IO uint32_t FGCMAR; /*!< DMA2D Foreground CLUT Memory Address Register, Address offset: 0x2C */ 15 __IO uint32_t BGCMAR; /*!< DMA2D Background CLUT Memory Address Register, Address offset: 0x30 */ 16 __IO uint32_t OPFCCR; /*!< DMA2D Output PFC Control Register, Address offset: 0x34 */ 17 __IO uint32_t OCOLR; /*!< DMA2D Output Color Register, Address offset: 0x38 */ 18 __IO uint32_t OMAR; /*!< DMA2D Output Memory Address Register, Address offset: 0x3C */ 19 __IO uint32_t OOR; /*!< DMA2D Output Offset Register, Address offset: 0x40 */ 20 __IO uint32_t NLR; /*!< DMA2D Number of Line Register, Address offset: 0x44 */ 21 __IO uint32_t LWR; /*!< DMA2D Line Watermark Register, Address offset: 0x48 */ 22 __IO uint32_t AMTCR; /*!< DMA2D AHB Master Timer Configuration Register, Address offset: 0x4C */ 23 uint32_t RESERVED[236]; /*!< Reserved, 0x50-0x3FF */ 24 __IO uint32_t FGCLUT[256]; /*!< DMA2D Foreground CLUT, Address offset:400-7FF */ 25 __IO uint32_t BGCLUT[256]; /*!< DMA2D Background CLUT, Address offset:800-BFF */ 26 } DMA2D_TypeDef;

1 /** 2 * @brief DMA2D Init structure definition 3 */ 4 typedef struct 5 { 6 uint32_t Mode; /*!< configures the DMA2D transfer mode. 7 This parameter can be one value of @ref DMA2D_Mode */ 8 9 uint32_t ColorMode; /*!< configures the color format of the output image. 10 This parameter can be one value of @ref DMA2D_Color_Mode */ 11 12 uint32_t OutputOffset; /*!< Specifies the Offset value. 13 This parameter must be a number between Min_Data = 0x0000 and Max_Data = 0x3FFF. */ 14 } DMA2D_InitTypeDef;

/* Configure the DMA2D Mode, Color Mode and output offset */

hdma2d_eval.Init.Mode = DMA2D_M2M_PFC; //DMA2D_CR DMA2D模式

hdma2d_eval.Init.ColorMode = DMA2D_ARGB8888; //DMA2D_OPFCCR 输出颜色模式

hdma2d_eval.Init.OutputOffset = 0; //DMA2D_OOR

这三个在上一篇中已经分析过这三个参数在HAL_DMA2D_Init(&hdma2d_eval)中执行

1 /** 2 * @brief Initializes the DMA2D according to the specified 3 * parameters in the DMA2D_InitTypeDef and create the associated handle. 4 * @param hdma2d: pointer to a DMA2D_HandleTypeDef structure that contains 5 * the configuration information for the DMA2D. 6 * @retval HAL status 7 */ 8 HAL_StatusTypeDef HAL_DMA2D_Init(DMA2D_HandleTypeDef *hdma2d) 9 { 10 uint32_t tmp = 0; 11 12 /* Check the DMA2D peripheral state */ 13 if(hdma2d == NULL) 14 { 15 return HAL_ERROR; 16 } 17 18 /* Check the parameters */ 19 assert_param(IS_DMA2D_ALL_INSTANCE(hdma2d->Instance)); 20 assert_param(IS_DMA2D_MODE(hdma2d->Init.Mode)); 21 assert_param(IS_DMA2D_CMODE(hdma2d->Init.ColorMode)); 22 assert_param(IS_DMA2D_OFFSET(hdma2d->Init.OutputOffset)); 23 24 if(hdma2d->State == HAL_DMA2D_STATE_RESET) 25 { 26 /* Allocate lock resource and initialize it */ 27 hdma2d->Lock = HAL_UNLOCKED; 28 /* Init the low level hardware */ 29 HAL_DMA2D_MspInit(hdma2d); 30 } 31 32 /* Change DMA2D peripheral state */ 33 hdma2d->State = HAL_DMA2D_STATE_BUSY; 34 35 /* DMA2D CR register configuration -------------------------------------------*/ 36 /* Get the CR register value */ 37 tmp = hdma2d->Instance->CR; 38 39 /* Clear Mode bits */ 40 tmp &= (uint32_t)~DMA2D_CR_MODE; 41 42 /* Prepare the value to be wrote to the CR register */ 43 tmp |= hdma2d->Init.Mode; 44 45 /* Write to DMA2D CR register */ 46 hdma2d->Instance->CR = tmp; 47 48 /* DMA2D OPFCCR register configuration ---------------------------------------*/ 49 /* Get the OPFCCR register value */ 50 tmp = hdma2d->Instance->OPFCCR; 51 52 /* Clear Color Mode bits */ 53 tmp &= (uint32_t)~DMA2D_OPFCCR_CM; 54 55 /* Prepare the value to be wrote to the OPFCCR register */ 56 tmp |= hdma2d->Init.ColorMode; 57 58 /* Write to DMA2D OPFCCR register */ 59 hdma2d->Instance->OPFCCR = tmp; 60 61 /* DMA2D OOR register configuration ------------------------------------------*/ 62 /* Get the OOR register value */ 63 tmp = hdma2d->Instance->OOR; 64 65 /* Clear Offset bits */ 66 tmp &= (uint32_t)~DMA2D_OOR_LO; 67 68 /* Prepare the value to be wrote to the OOR register */ 69 tmp |= hdma2d->Init.OutputOffset; 70 71 /* Write to DMA2D OOR register */ 72 hdma2d->Instance->OOR = tmp; 73 74 /* Update error code */ 75 hdma2d->ErrorCode = HAL_DMA2D_ERROR_NONE; 76 77 /* Initialize the DMA2D state*/ 78 hdma2d->State = HAL_DMA2D_STATE_READY; 79 80 return HAL_OK; 81 }

hdma2d_eval.Instance = DMA2D;

DMA2D_TypeDef *Instance;

#define DMA2D ((DMA2D_TypeDef *)DMA2D_BASE)

这里是指向DMA2D的寄存器

1 /** 2 * @brief DMA2D Layer structure definition 3 */ 4 typedef struct 5 { 6 uint32_t InputOffset; /*!< configures the DMA2D foreground offset. 7 This parameter must be a number between Min_Data = 0x0000 and Max_Data = 0x3FFF. */ 8 9 uint32_t InputColorMode; /*!< configures the DMA2D foreground color mode . 10 This parameter can be one value of @ref DMA2D_Input_Color_Mode */ 11 12 uint32_t AlphaMode; /*!< configures the DMA2D foreground alpha mode. 13 This parameter can be one value of @ref DMA2D_ALPHA_MODE */ 14 15 uint32_t InputAlpha; /*!< Specifies the DMA2D foreground alpha value and color value in case of A8 or A4 color mode. 16 This parameter must be a number between Min_Data = 0x00000000 and Max_Data = 0xFFFFFFFF 17 in case of A8 or A4 color mode (ARGB). 18 Otherwise, This parameter must be a number between Min_Data = 0x00 and Max_Data = 0xFF.*/ 19 20 } DMA2D_LayerCfgTypeDef;

/* Foreground Configuration */

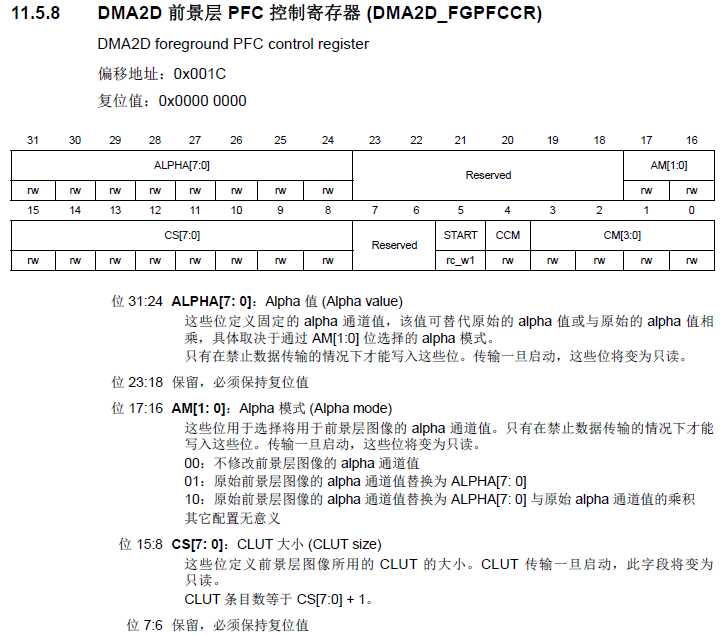

hdma2d_eval.LayerCfg[1].AlphaMode = DMA2D_NO_MODIF_ALPHA; //DMA2D_FGPFCCR

hdma2d_eval.LayerCfg[1].InputAlpha = 0xFF; //DMA2D_FGPFCCR

hdma2d_eval.LayerCfg[1].InputColorMode = CM_RGB565; //DMA2D_FGPFCCR

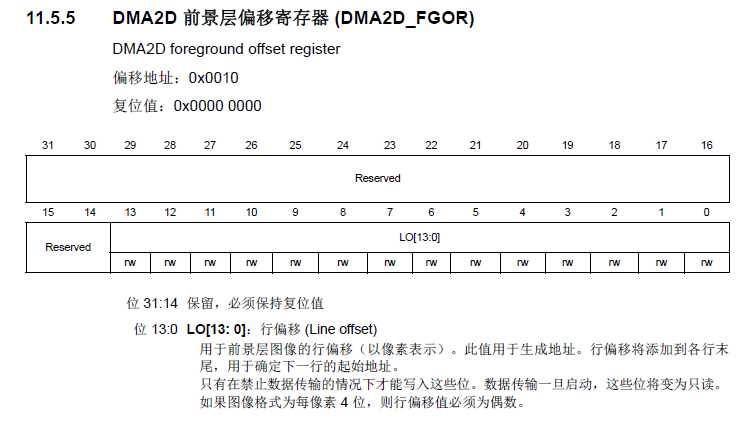

hdma2d_eval.LayerCfg[1].InputOffset = 0; //DMA2D_FGOR

前景色的配置,由摄像头输入,配置了透明度和颜色模式与偏移

设置函数:HAL_DMA2D_ConfigLayer(&hdma2d_eval, 1)

1 /** 2 * @brief Configure the DMA2D Layer according to the specified 3 * parameters in the DMA2D_InitTypeDef and create the associated handle. 4 * @param hdma2d: pointer to a DMA2D_HandleTypeDef structure that contains 5 * the configuration information for the DMA2D. 6 * @param LayerIdx: DMA2D Layer index. 7 * This parameter can be one of the following values: 8 * 0(background) / 1(foreground) 9 * @retval HAL status 10 */ 11 HAL_StatusTypeDef HAL_DMA2D_ConfigLayer(DMA2D_HandleTypeDef *hdma2d, uint32_t LayerIdx) 12 { 13 DMA2D_LayerCfgTypeDef *pLayerCfg = &hdma2d->LayerCfg[LayerIdx]; 14 15 uint32_t tmp = 0; 16 17 /* Process locked */ 18 __HAL_LOCK(hdma2d); 19 20 /* Change DMA2D peripheral state */ 21 hdma2d->State = HAL_DMA2D_STATE_BUSY; 22 23 /* Check the parameters */ 24 assert_param(IS_DMA2D_LAYER(LayerIdx)); 25 assert_param(IS_DMA2D_OFFSET(pLayerCfg->InputOffset)); 26 if(hdma2d->Init.Mode != DMA2D_R2M) 27 { 28 assert_param(IS_DMA2D_INPUT_COLOR_MODE(pLayerCfg->InputColorMode)); 29 if(hdma2d->Init.Mode != DMA2D_M2M) 30 { 31 assert_param(IS_DMA2D_ALPHA_MODE(pLayerCfg->AlphaMode)); 32 } 33 } 34 35 /* Configure the background DMA2D layer */ 36 if(LayerIdx == 0) 37 { 38 /* DMA2D BGPFCR register configuration -----------------------------------*/ 39 /* Get the BGPFCCR register value */ 40 tmp = hdma2d->Instance->BGPFCCR; 41 42 /* Clear Input color mode, alpha value and alpha mode bits */ 43 tmp &= (uint32_t)~(DMA2D_BGPFCCR_CM | DMA2D_BGPFCCR_AM | DMA2D_BGPFCCR_ALPHA); 44 45 if ((pLayerCfg->InputColorMode == CM_A4) || (pLayerCfg->InputColorMode == CM_A8)) 46 { 47 /* Prepare the value to be wrote to the BGPFCCR register */ 48 tmp |= (pLayerCfg->InputColorMode | (pLayerCfg->AlphaMode << 16) | ((pLayerCfg->InputAlpha) & 0xFF000000)); 49 } 50 else 51 { 52 /* Prepare the value to be wrote to the BGPFCCR register */ 53 tmp |= (pLayerCfg->InputColorMode | (pLayerCfg->AlphaMode << 16) | (pLayerCfg->InputAlpha << 24)); 54 } 55 56 /* Write to DMA2D BGPFCCR register */ 57 hdma2d->Instance->BGPFCCR = tmp; 58 59 /* DMA2D BGOR register configuration -------------------------------------*/ 60 /* Get the BGOR register value */ 61 tmp = hdma2d->Instance->BGOR; 62 63 /* Clear colors bits */ 64 tmp &= (uint32_t)~DMA2D_BGOR_LO; 65 66 /* Prepare the value to be wrote to the BGOR register */ 67 tmp |= pLayerCfg->InputOffset; 68 69 /* Write to DMA2D BGOR register */ 70 hdma2d->Instance->BGOR = tmp; 71 72 if ((pLayerCfg->InputColorMode == CM_A4) || (pLayerCfg->InputColorMode == CM_A8)) 73 { 74 /* Prepare the value to be wrote to the BGCOLR register */ 75 tmp |= ((pLayerCfg->InputAlpha) & 0x00FFFFFF); 76 77 /* Write to DMA2D BGCOLR register */ 78 hdma2d->Instance->BGCOLR = tmp; 79 } 80 } 81 /* Configure the foreground DMA2D layer */ 82 else 83 { 84 /* DMA2D FGPFCR register configuration -----------------------------------*/ 85 /* Get the FGPFCCR register value */ 86 tmp = hdma2d->Instance->FGPFCCR; 87 88 /* Clear Input color mode, alpha value and alpha mode bits */ 89 tmp &= (uint32_t)~(DMA2D_FGPFCCR_CM | DMA2D_FGPFCCR_AM | DMA2D_FGPFCCR_ALPHA); 90 91 if ((pLayerCfg->InputColorMode == CM_A4) || (pLayerCfg->InputColorMode == CM_A8)) 92 { 93 /* Prepare the value to be wrote to the FGPFCCR register */ 94 tmp |= (pLayerCfg->InputColorMode | (pLayerCfg->AlphaMode << 16) | ((pLayerCfg->InputAlpha) & 0xFF000000)); 95 } 96 else 97 { 98 /* Prepare the value to be wrote to the FGPFCCR register */ 99 tmp |= (pLayerCfg->InputColorMode | (pLayerCfg->AlphaMode << 16) | (pLayerCfg->InputAlpha << 24)); 100 } 101 102 /* Write to DMA2D FGPFCCR register */ 103 hdma2d->Instance->FGPFCCR = tmp; 104 105 /* DMA2D FGOR register configuration -------------------------------------*/ 106 /* Get the FGOR register value */ 107 tmp = hdma2d->Instance->FGOR; 108 109 /* Clear colors bits */ 110 tmp &= (uint32_t)~DMA2D_FGOR_LO; 111 112 /* Prepare the value to be wrote to the FGOR register */ 113 tmp |= pLayerCfg->InputOffset; 114 115 /* Write to DMA2D FGOR register */ 116 hdma2d->Instance->FGOR = tmp; 117 118 if ((pLayerCfg->InputColorMode == CM_A4) || (pLayerCfg->InputColorMode == CM_A8)) 119 { 120 /* Prepare the value to be wrote to the FGCOLR register */ 121 tmp |= ((pLayerCfg->InputAlpha) & 0x00FFFFFF); 122 123 /* Write to DMA2D FGCOLR register */ 124 hdma2d->Instance->FGCOLR = tmp; 125 } 126 } 127 /* Initialize the DMA2D state*/ 128 hdma2d->State = HAL_DMA2D_STATE_READY; 129 130 /* Process unlocked */ 131 __HAL_UNLOCK(hdma2d); 132 133 return HAL_OK; 134 }

可以看到FG和BG是输入数据源,所以这些是对输入数据的设置

1 /** 2 * @brief Start the DMA2D Transfer. 3 * @param hdma2d: pointer to a DMA2D_HandleTypeDef structure that contains 4 * the configuration information for the DMA2D. 5 * @param pdata: Configure the source memory Buffer address if 6 * the memory to memory or memory to memory with pixel format 7 * conversion DMA2D mode is selected, and configure 8 * the color value if register to memory DMA2D mode is selected. 9 * @param DstAddress: The destination memory Buffer address. 10 * @param Width: The width of data to be transferred from source to destination. 11 * @param Height: The height of data to be transferred from source to destination. 12 * @retval HAL status 13 */ 14 HAL_StatusTypeDef HAL_DMA2D_Start(DMA2D_HandleTypeDef *hdma2d, uint32_t pdata, uint32_t DstAddress, uint32_t Width, uint32_t Height) 15 { 16 /* Process locked */ 17 __HAL_LOCK(hdma2d); 18 19 /* Change DMA2D peripheral state */ 20 hdma2d->State = HAL_DMA2D_STATE_BUSY; 21 22 /* Check the parameters */ 23 assert_param(IS_DMA2D_LINE(Height)); 24 assert_param(IS_DMA2D_PIXEL(Width)); 25 26 /* Disable the Peripheral */ 27 __HAL_DMA2D_DISABLE(hdma2d); 28 29 /* Configure the source, destination address and the data size */ 30 DMA2D_SetConfig(hdma2d, pdata, DstAddress, Width, Height); 31 32 /* Enable the Peripheral */ 33 __HAL_DMA2D_ENABLE(hdma2d); 34 35 return HAL_OK; 36 }

1 /** 2 * @brief Set the DMA2D Transfer parameter. 3 * @param hdma2d: pointer to a DMA2D_HandleTypeDef structure that contains 4 * the configuration information for the specified DMA2D. 5 * @param pdata: The source memory Buffer address 6 * @param DstAddress: The destination memory Buffer address 7 * @param Width: The width of data to be transferred from source to destination. 8 * @param Height: The height of data to be transferred from source to destination. 9 * @retval HAL status 10 */ 11 static void DMA2D_SetConfig(DMA2D_HandleTypeDef *hdma2d, uint32_t pdata, uint32_t DstAddress, uint32_t Width, uint32_t Height) 12 { 13 uint32_t tmp = 0; 14 uint32_t tmp1 = 0; 15 uint32_t tmp2 = 0; 16 uint32_t tmp3 = 0; 17 uint32_t tmp4 = 0; 18 19 tmp = Width << 16; 20 21 /* Configure DMA2D data size */ 22 hdma2d->Instance->NLR = (Height | tmp); 23 24 /* Configure DMA2D destination address */ 25 hdma2d->Instance->OMAR = DstAddress; 26 27 /* Register to memory DMA2D mode selected */ 28 if (hdma2d->Init.Mode == DMA2D_R2M) 29 { 30 tmp1 = pdata & DMA2D_OCOLR_ALPHA_1; 31 tmp2 = pdata & DMA2D_OCOLR_RED_1; 32 tmp3 = pdata & DMA2D_OCOLR_GREEN_1; 33 tmp4 = pdata & DMA2D_OCOLR_BLUE_1; 34 35 /* Prepare the value to be wrote to the OCOLR register according to the color mode */ 36 if (hdma2d->Init.ColorMode == DMA2D_ARGB8888) 37 { 38 tmp = (tmp3 | tmp2 | tmp1| tmp4); 39 } 40 else if (hdma2d->Init.ColorMode == DMA2D_RGB888) 41 { 42 tmp = (tmp3 | tmp2 | tmp4); 43 } 44 else if (hdma2d->Init.ColorMode == DMA2D_RGB565) 45 { 46 tmp2 = (tmp2 >> 19); 47 tmp3 = (tmp3 >> 10); 48 tmp4 = (tmp4 >> 3 ); 49 tmp = ((tmp3 << 5) | (tmp2 << 11) | tmp4); 50 } 51 else if (hdma2d->Init.ColorMode == DMA2D_ARGB1555) 52 { 53 tmp1 = (tmp1 >> 31); 54 tmp2 = (tmp2 >> 19); 55 tmp3 = (tmp3 >> 11); 56 tmp4 = (tmp4 >> 3 ); 57 tmp = ((tmp3 << 5) | (tmp2 << 10) | (tmp1 << 15) | tmp4); 58 } 59 else /* DMA2D_CMode = DMA2D_ARGB4444 */ 60 { 61 tmp1 = (tmp1 >> 28); 62 tmp2 = (tmp2 >> 20); 63 tmp3 = (tmp3 >> 12); 64 tmp4 = (tmp4 >> 4 ); 65 tmp = ((tmp3 << 4) | (tmp2 << 8) | (tmp1 << 12) | tmp4); 66 } 67 /* Write to DMA2D OCOLR register */ 68 hdma2d->Instance->OCOLR = tmp; 69 } 70 else /* M2M, M2M_PFC or M2M_Blending DMA2D Mode */ 71 { 72 /* Configure DMA2D source address */ 73 hdma2d->Instance->FGMAR = pdata; 74 } 75 }

/* Configure DMA2D data size */

tmp = Width << 16;

hdma2d->Instance->NLR = (Height | tmp);

/* Configure DMA2D destination address */

hdma2d->Instance->OMAR = DstAddress;

/* Configure DMA2D source address */

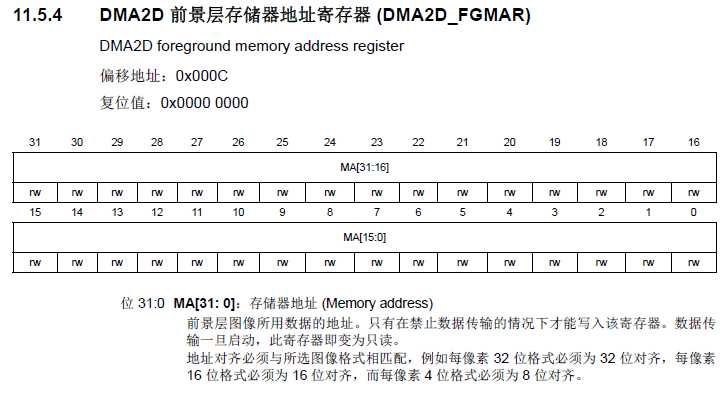

hdma2d->Instance->FGMAR = pdata;

这里设置两边memory的地址与行数也就是数据量

DMA2D_NLR 与DMA2D_OMAR 前面一章介绍过

整个初始化流程结束,主要设置了output,源地址是FG

最后设置传输:

1 /** 2 * @brief Polling for transfer complete or CLUT loading. 3 * @param hdma2d: pointer to a DMA2D_HandleTypeDef structure that contains 4 * the configuration information for the DMA2D. 5 * @param Timeout: Timeout duration 6 * @retval HAL status 7 */ 8 HAL_StatusTypeDef HAL_DMA2D_PollForTransfer(DMA2D_HandleTypeDef *hdma2d, uint32_t Timeout) 9 { 10 uint32_t tmp, tmp1; 11 uint32_t tickstart = 0; 12 13 /* Polling for DMA2D transfer */ 14 if((hdma2d->Instance->CR & DMA2D_CR_START) != 0) 15 { 16 /* Get tick */ 17 tickstart = HAL_GetTick(); 18 19 while(__HAL_DMA2D_GET_FLAG(hdma2d, DMA2D_FLAG_TC) == RESET) 20 { 21 tmp = __HAL_DMA2D_GET_FLAG(hdma2d, DMA2D_FLAG_CE); 22 tmp1 = __HAL_DMA2D_GET_FLAG(hdma2d, DMA2D_FLAG_TE); 23 24 if((tmp != RESET) || (tmp1 != RESET)) 25 { 26 /* Clear the transfer and configuration error flags */ 27 __HAL_DMA2D_CLEAR_FLAG(hdma2d, DMA2D_FLAG_CE); 28 __HAL_DMA2D_CLEAR_FLAG(hdma2d, DMA2D_FLAG_TE); 29 30 /* Change DMA2D state */ 31 hdma2d->State= HAL_DMA2D_STATE_ERROR; 32 33 /* Process unlocked */ 34 __HAL_UNLOCK(hdma2d); 35 36 return HAL_ERROR; 37 } 38 /* Check for the Timeout */ 39 if(Timeout != HAL_MAX_DELAY) 40 { 41 if((Timeout == 0)||((HAL_GetTick() - tickstart ) > Timeout)) 42 { 43 /* Process unlocked */ 44 __HAL_UNLOCK(hdma2d); 45 46 /* Update error code */ 47 hdma2d->ErrorCode |= HAL_DMA2D_ERROR_TIMEOUT; 48 49 /* Change the DMA2D state */ 50 hdma2d->State= HAL_DMA2D_STATE_TIMEOUT; 51 52 return HAL_TIMEOUT; 53 } 54 } 55 } 56 } 57 /* Polling for CLUT loading */ 58 if((hdma2d->Instance->FGPFCCR & DMA2D_FGPFCCR_START) != 0) 59 { 60 /* Get tick */ 61 tickstart = HAL_GetTick(); 62 63 while(__HAL_DMA2D_GET_FLAG(hdma2d, DMA2D_FLAG_CTC) == RESET) 64 { 65 if((__HAL_DMA2D_GET_FLAG(hdma2d, DMA2D_FLAG_CAE) != RESET)) 66 { 67 /* Clear the transfer and configuration error flags */ 68 __HAL_DMA2D_CLEAR_FLAG(hdma2d, DMA2D_FLAG_CAE); 69 70 /* Change DMA2D state */ 71 hdma2d->State= HAL_DMA2D_STATE_ERROR; 72 73 return HAL_ERROR; 74 } 75 /* Check for the Timeout */ 76 if(Timeout != HAL_MAX_DELAY) 77 { 78 if((Timeout == 0)||((HAL_GetTick() - tickstart ) > Timeout)) 79 { 80 /* Update error code */ 81 hdma2d->ErrorCode |= HAL_DMA2D_ERROR_TIMEOUT; 82 83 /* Change the DMA2D state */ 84 hdma2d->State= HAL_DMA2D_STATE_TIMEOUT; 85 86 return HAL_TIMEOUT; 87 } 88 } 89 } 90 } 91 /* Clear the transfer complete flag */ 92 __HAL_DMA2D_CLEAR_FLAG(hdma2d, DMA2D_FLAG_TC); 93 94 /* Clear the CLUT loading flag */ 95 __HAL_DMA2D_CLEAR_FLAG(hdma2d, DMA2D_FLAG_CTC); 96 97 /* Change DMA2D state */ 98 hdma2d->State = HAL_DMA2D_STATE_READY; 99 100 /* Process unlocked */ 101 __HAL_UNLOCK(hdma2d); 102 103 return HAL_OK; 104 }

#define DMA2D_FLAG_CE DMA2D_ISR_CEIF /*!< Configuration Error Interrupt Flag */

#define DMA2D_FLAG_CTC DMA2D_ISR_CTCIF /*!< C-LUT Transfer Complete Interrupt Flag */

#define DMA2D_FLAG_CAE DMA2D_ISR_CAEIF /*!< C-LUT Access Error Interrupt Flag */

#define DMA2D_FLAG_TW DMA2D_ISR_TWIF /*!< Transfer Watermark Interrupt Flag */

#define DMA2D_FLAG_TC DMA2D_ISR_TCIF /*!< Transfer Complete Interrupt Flag */

#define DMA2D_FLAG_TE DMA2D_ISR_TEIF /*!< Transfer Error Interrupt Flag */

标签:

原文地址:http://www.cnblogs.com/wwjdwy/p/4604820.html