标签:

?第一章

1.?比较数字计算机和模拟计算机的特点。

解:模拟计算机的特点:数值由连续量来表示,运算过程是连续的;

数字计算机的特点:数值由数字量(离散量)来表示,运算按位进行。

两者主要区别见P1?表1.1。

2.?数字计算机如何分类?分类的依据是什么?

解:分类: 数字计算机分为专用计算机和通用计算机。通用计算机又分为巨型机、大型机、

中型机、小型机、微型机和单片机六类。

分类依据:专用和通用是根据计算机的效率、速度、价格、运行的经济性和适应性来划分的。

通用机的分类依据主要是体积、简易性、功率损耗、性能指标、数据存储容量、

指令系统规模和机器价格等因素。

3.?数字计算机有那些主要应用?

(略)

4.?冯.?诺依曼型计算机的主要设计思想是什么?它包括哪些主要组成部分?

解:冯.?诺依曼型计算机的主要设计思想是:存储程序和程序控制。

存储程序:将解题的程序(指令序列)存放到存储器中;

程序控制:控制器顺序执行存储的程序,按指令功能控制全机协调地完成运算任务。

主要组成部分有:控制器、运算器、存储器、输入设备、输出设备。

5.?什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?

解:存储容量:指存储器可以容纳的二进制信息的数量,通常用单位KB、MB、GB来度量,存储容

量越大,表示计算机所能存储的信息量越多,反映了计算机存储空间的大小。

单元地址:单元地址简称地址,在存储器中每个存储单元都有唯一的地址编号,称为单元地

址。

数据字:?若某计算机字是运算操作的对象即代表要处理的数据,则称数据字。

指令字:?若某计算机字代表一条指令或指令的一部分,则称指令字。?

6.?什么是指令?什么是程序?

解:指令:计算机所执行的每一个基本的操作。

程序:解算某一问题的一串指令序列称为该问题的计算程序,简称程序。?

7.?指令和数据均存放在内存中,计算机如何区分它们是指令还是数据?

解:一般来讲,在取指周期中从存储器读出的信息即指令信息;而在执行周期中从存储器中读出的

信息即为数据信息。

8.?什么是内存?什么是外存?什么是CPU?什么是适配器?简述其功能。

解:内存:一般由半导体存储器构成,装在底版上,可直接和CPU交换信息的存储器称为内存储

器,简称内存。用来存放经常使用的程序和数据。

外存:为了扩大存储容量,又不使成本有很大的提高,在计算机中还配备了存储容量更大的

磁盘存储器和光盘存储器,称为外存储器,简称外存。外存可存储大量的信息,计算

机需要使用时,再调入内存。?

CPU:包括运算器和控制器。基本功能为:指令控制、操作控制、时间控制、数据加工。

适配器:连接主机和外设的部件,起一个转换器的作用,以使主机和外设协调工作。?

9.?计算机的系统软件包括哪几类?说明它们的用途。

解:系统软件包括:(1)服务程序:诊断、排错等

(2)语言程序:汇编、编译、解释等

(3)操作系统

(4)数据库管理系统

用途:用来简化程序设计,简化使用方法,提高计算机的使用效率,发挥和扩大计算机的功能

及用途。?

10.?说明软件发展的演变过程。

(略)

11.?现代计算机系统如何进行多级划分?这种分级观点对计算机设计会产生什么影响?

解:多级划分图见P16图1.6。可分为:微程序设计级、一般机器级、操作系统级、汇编语言级和

高级语言级。

用这种分级的观点来设计计算机,对保证产生一个良好的系统结构是有很大帮助的。

12.?为什么软件能够转化为硬件?硬件能够转化为软件?实现这种转化的媒介是什么?

(略)

13.?"计算机应用"与"应用计算机"在概念上等价吗?用学科角度和计算机系统的层次结构来寿命你的观点。?

(略)

第二章

1.?写出下列各数的原码、反码、补码、移码表示(用8位二进制数)。其中MSB是最高位(又是符号位)LSB是最低位。如果是小数,小数点在MSB之后;如果是整数,小数点在LSB之后。

(1)?-35/64?(2)?23/128?(3)?-127?(4)?用小数表示-1?(5)?用整数表示-1

解:(1)先把十进制数-35/64写成二进制小数:

(-35/64)10=(-100011/1000000)2=(-100011×2-110)2=(-0.100011)2

令x=-0.100011B

∴?[x]原=1.1000110?(注意位数为8位)?[x]反=1.0111001

?[x]补=1.0111010? [x]移=0.0111010

(2)?先把十进制数23/128写成二进制小数:

(23/128)10=(10111/10000000)2=(10111×2-111)2=(0.0001011)2

令x=0.0001011B

∴?[x]原=0.0001011? [x]反=0.0001011

?[x]补=0.0001011? [x]移=1.0001011

(3)?先把十进制数-127写成二进制小数:

(-127)10=(-1111111)2

令x=?-1111111B

∴?[x]原=1.1111111? [x]反=1.0000000

?[x]补=1.0000001? [x]移=1.0000001

(4)?令x=-1.000000B

∴?原码、反码无法表示

[x]补=1.0000000? ?[x]移=0.0000000

(5)?令Y=-1=-0000001B

∴?[Y]原=10000001? ?[Y]反=11111110

?[Y]补=11111111? ?[Y]移=01111111

2.?设[X]补=?a0,a1,a2…a6?,?其中ai取0或1,若要x>-0.5,求a0,a1,a2,…,a6?的取值。

解:a0=?1,a1=?0,?a2,…,a6=1…1。

3.?有一个字长为32位的浮点数,阶码10位(包括1位阶符),用移码表示;尾数22位(包括1位尾符)用补码表示,基数R=2。请写出:

(1)?最大数的二进制表示;

(2)?最小数的二进制表示;

(3)?规格化数所能表示的数的范围;

(4)?最接近于零的正规格化数与负规格化数。

解:(1)1111111111?0111111111111111111111

(2)1111111111?1000000000000000000000

(3)1111111111?0111111111111111111111~0111111111?1000000000000000000000

(4)0000000000?0000000000000000000001~0000000000?1111111111111111111111

4.?将下列十进制数表示成浮点规格化数,阶码3位,用补码表示;尾数9位,用补码表示。

(1)?27/64

(2)?-27/64

解:(1)27/64=11011B×![]() =0.011011B=0.11011B×

=0.011011B=0.11011B×![]()

浮点规格化数?:?1111?0110110000

(2)?-27/64=?-11011B×![]() =?-0.011011B=?-0.11011B×

=?-0.011011B=?-0.11011B×![]()

浮点规格化数?:?1111?1001010000

5.?已知X和Y,?用变形补码计算X+Y,?同时指出运算结果是否溢出。

(1)X=0.11011?Y=0.00011

(2)X=?0.11011?Y=?-0.10101

(3)X=-0.10110?Y=-0.00001

解:(1)先写出x和y的变形补码再计算它们的和

[x]补=00.11011?[y]补=00.00011

[x+y]补=[x]补+[y]补=00.11011+00.00011=0.11110

∴?x+y=0.1111B?无溢出。

(2)先写出x和y的变形补码再计算它们的和

[x]补=00.11011?[y]补=11.01011

[x+y]补=[x]补+[y]补=00.11011+11.01011=00.00110

∴?x+y=0.0011B?无溢出。

(3)先写出x和y的变形补码再计算它们的和?

[x]补=11.01010?[y]补=11.11111

[x+y]补=[x]补+[y]补=11.01010+11.11111=11.01001

∴?x+y=?-0.10111B?无溢出

6.?已知X和Y,?用变形补码计算X-Y,?同时指出运算结果是否溢出。

(1)?X=0.11011?Y=?-0.11111

(2)?X=0.10111?Y=0.11011

(3)?X=0.11011?Y=-0.10011

解:(1)先写出x和y的变形补码,再计算它们的差

[x]补=00.11011?[y]补=11.00001?[-y]补=00.11111

[x-y]补=[x]补+[-y]补=00.11011+00.11111=01.11010

∵运算结果双符号不相等?∴?为正溢出

X-Y=+1.1101B

(2)先写出x和y的变形补码,再计算它们的差

[x]补=00.10111?[y]补=00.11011?[-y]补=11.00101

[x-y]补=00.10111+11.00101=11.11100

∴?x-y=?-0.001B?无溢出

(3)先写出x和y的变形补码,再计算它们的差

[x]补=00.11011?[y]补=11.01101?[-y]补=00.10011

[x-y]补=[x]补+[-y]补=00.11011+00.10011=01.01110

∵运算结果双符号不相等?∴?为正溢出

X-Y=+1.0111B

7.?用原码阵列乘法器、补码阵列乘法器分别计算X×Y。

(1)X=0.11011?Y=?-0.11111

(2)X=-0.11111?Y=-0.11011?

解:(1)用原码阵列乘法器计算:

[x]补=0.11011?[y]补=1.00001

(0) 1? 1? 0? 1? 1?

×)?(1) 0? 0? 0? 0? 1?

----------------------------------

(0) 1? 1? 0? 1? 1

(0) 0? 0? 0? 0? 0?

?(0) 0? 0? 0? 0? 0?

(0) 0? 0? 0? 0? 0

(0) 0? 0? 0? 0? 0

(0)?(1)?(1)?(0)?(1)?(1)

-----------------------------------------

(1) 0? 0? 1? 0? 1? 1? 1? 0? 1? 1?

[x×y]补=1.0010111011

∴?x×y=?-0.1101000101

8.?用原码阵列除法器计算?X÷Y。

(1)X=0.11000?Y=?-0.11111

(2)X=-0.01011?Y=0.11001

解:(1)[x]原=[x]补=0.11000? [-∣y∣]补=1.00001

? 被除数?X 0.11000

?+[-∣y∣]补?1.00001

----------------------

余数为负?1.11001?→q0=0

左移?1.10010

?+[|y|]补 0.11111

----------------------

余数为正?0.10001?→q1=1

左移?1.00010?

? +[-|y|]补?1.00001

----------------------

余数为正?0.00011?→q2=1?

? ?左移?0.00110?

? +[-|y|]补?1.00001

----------------------

余数为负?1.00111?→q3=0

左移?0.01110

?+[|y|]补 0.11111

----------------------

余数为负?1.01101?→q4=0

左移?0.11010

?+[|y|]补 0.11111

----------------------

余数为负?1.11001?→q5=0

?+[|y|]补 0.11111

----------------------

余数?0.11000

故?[x÷y]原=1.11000?即?x÷y=?-0.11000B

余数为?0.11000B×![]()

9.?设阶为5位(包括2位阶符),?尾数为8位(包括2位数符),?阶码、尾数均用补码表示,?完成下列取值的[X+Y],[X-Y]运算:

(1)X=![]() ×0.100101?Y=

×0.100101?Y=![]() ×(-0.011110)

×(-0.011110)

(2)X=![]() ×(-0.010110)?Y=

×(-0.010110)?Y=![]() ×(0.010110)

×(0.010110)

解:(1)将y规格化得:y=![]() ×(-0.111100)

×(-0.111100)

[x]浮=1101,00.100101?[y]浮=1101,11.000100?[-y]浮=1101,00.111100

①?对阶

[ΔE]补=[Ex]补+[-Ey]补=1101+0011=0000

∴?Ex=Ey

②?尾数相加?

相加? 相减

00.100101? ? 00.100101

+?11.000100? ? +?00.111100

------------? --------------

11.101001? ?01.100001

[x+y]浮=1101,11.101001? 左规?[x+y]浮=1100,11.010010?

∴?x+y=![]() ×(-0.101110)?

×(-0.101110)?

[x-y]浮=1101,01.100001? 右规?[x-y]浮=1110,00.1100001

舍入处理得?[x-y]浮=1110,00.110001?

∴?x-y=![]() ×0.110001

×0.110001

(2)?[x]浮=1011,11.101010?[y]浮=1100,00.010110?[-y]浮=1100,11.101010

①?对阶

[ΔE]补=[Ex]补+[-Ey]补=1011+0100=1111

∴?△E=?-1?[x]浮=1100,11.110101(0)?

②?尾数相加

相加? 相减

11.110101(0)? 11.110101(0)

+?00.010110? ?+?11.101010

-------------- ------------------

00.001011(0)? 11.011111(0)

[x+y]浮=1100,00.001011(0)?左规?[x+y]浮=1010,00.1011000?

∴?x+y=![]() ×0.1011B

×0.1011B

[x-y]浮=1100,11.011111(0)?

∴?x-y=![]() ×(-0.100001B)

×(-0.100001B)

13.?某加法器进位链小组信号为C4C3C2C1?,低位来的信号为C0?,请分别按下述两种方式写出C4C3C2C1的逻辑表达式。

(1)?串行进位方式?(2)?并行进位方式

解?:(1)串行进位方式:

C1?=?G1?+?P1?C0?其中:?G1?=?A1?B1?,?P1?=?A1⊕B1

C2?=?G2?+?P2?C1? ?G2?=?A2?B2?,?P2?=?A2⊕B2

C3?=?G3?+?P3?C2? ?G3?=?A3?B3?,?P3?=?A3⊕B3

C4?=?G4?+?P4?C3? ?G4?=?A4?B4?,?P4?=?A4⊕B4

(2)?并行进位方式:

C1?=?G1?+?P1?C0?

C2?=?G2?+?P2?G1?+?P2?P1?C0

C3?=?G3?+?P3?G2?+?P3?P2?G1?+?P3?P2?P1?C0

C4?=?G4?+?P4?G3?+?P4?P3?G2?+?P4?P3?P2?G1?+?P4?P3?P2?P1?C0

其中?G1-G4?,P1-P4?表达式与串行进位方式相同。

14.?某机字长16位,使用四片74181组成ALU,设最低位序标注为0位,要求:

(1)写出第5位的进位信号C6的逻辑表达式;

(2)估算产生C6所需的最长时间;?

(3)估算最长的求和时间。

解:(1)?组成最低四位的74181进位输出为:C4=G+P?C0?,C0为向第0位的进位

其中:G=y3+x3y2+x2x3y1+x1x2x3y0,?P=x0x1x2x3

所以?:C5=y4+x4C4

C6=y5+x5C5=y5+x5y4+x5x4C4

(2)?设标准门延迟时间为T,"与或非"门延迟时间为1.5T,则进位信号C0由最低位传送至C6需经一个反相器,两级"与或非"门,故产生C6的最长延迟时间为:

T+2×1.5T=4T

(3)最长求和时间应从施加操作数到ALU算起:第一片74181有3级"与或非"门(产生控制参数x0,y0Cn+4),第二、第三片74181共2级反相器和2级"与或非"门(进位链),第四片74181求和逻辑(1级"与或非"门和1级半加器,其延迟时间为3T),故总的加法时间为:

T=3×1.5T+2T+2×1.5T+1.5T+1.5T+3T=14T

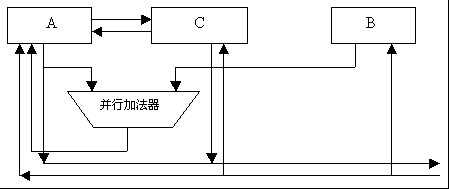

17.设A,B,C是三个16位的通用寄存器,请设计一个16位定点补码运算器,能实现下述功能:

(1)?A±B→A

(2)?B×C→A,?C(高位积在寄存器A中)

(3)?A÷B→C(商在寄存器C中)

解:设计能完成加、减、乘、除运算的16位定点补码运算器框图。

分析各寄存器作用:

加? ? 减? 乘? 除

A? 被加数→和? 同左? 初始为0? 被除数→余数

部分积→乘积(H) 除数

B? 加数? 同左? 被乘数

C --? --? 乘数→乘积(L)? 商

∴?A:累加器(16位),具有输入、输出、累加功能及双向移位功能;

?B:数据寄存器(16位),具有输入、输出功能;

?C:乘商寄存器(16位),具有输入、输出功能及双向移位功能。

画出框图:

第三章

1.有一个具有20位地址和32位字长的存储器,问:

(1)?该存储器能存储多少个字节的信息?

(2)?如果存储器由512K×8位SRAM芯片组成,需要多少芯片?

(3)?需要多少位地址作芯片选择?

解:(1)∵?220=?1M,?∴?该存储器能存储的信息为:1M×32/8=4MB

(2)(1000/512)×(32/8)=?8(片)

(3)?需要1位地址作为芯片选择。

2.?已知某64位机主存采用半导体存储器,其地址码为26位,若使用256K×16位的DRAM芯片组成该机所允许的最大主存空间,并选用模块板结构形式,问:

(1)?每个模块板为1024K×64位,共需几个模块板?

(2)?个模块板内共有多少DRAM芯片?

(3)主存共需多少DRAM芯片??CPU如何选择各模块板?

解:(1). 共需模块板数为m:

m=![]() ÷

÷![]() =64?(块)

=64?(块)

(2).?每个模块板内有DRAM芯片数为n:

n=(![]() /

/![]() )?×(64/16)=16?(片)

)?×(64/16)=16?(片)

(3)?主存共需DRAM芯片为:16×64=1024?(片)

每个模块板有16片DRAM芯片,容量为1024K×64位,需20根地址线(A19~A0)完成模块

板内存储单元寻址。一共有64块模块板,采用6根高位地址线(A25~A20),通过

6:64译码器译码产生片选信号对各模块板进行选择。

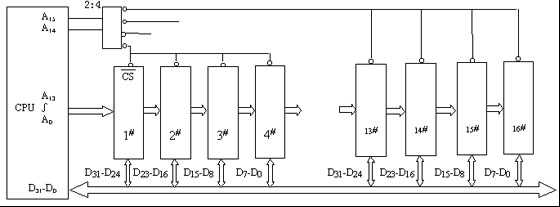

3.?用16K×8位的DRAM芯片组成64K×32位存储器,要求:

(1)?画出该存储器的组成逻辑框图。

(2)?设存储器读/写周期为0.5μS,?CPU在1μS内至少要访问一次。试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?

解:(1)组成64K×32位存储器需存储芯片数为

N=(64K/16K)×(32位/8位)=16(片)

?每4片组成16K×32位的存储区,有A13-A0作为片内地址,用A15?A14经2:4译码器产生片选信号![]() ?,逻辑框图如下所示:

?,逻辑框图如下所示:

(2)依题意,采用异步刷新方式较合理,可满足CPU在1μS内至少访问内存一次的要求。

?设16K×8位存储芯片的阵列结构为128行×128列,按行刷新,刷新周期T=2ms,则异步

?刷新的间隔时间为:

![]()

?则两次刷新的最大时间间隔发生的示意图如下

![]()

可见,两次刷新的最大时间间隔为tmax

tmax=15.5-0.5=15?(μS)

对全部存储单元刷新一遍所需时间为t?R

t?R?=0.5×128=64? (μS)

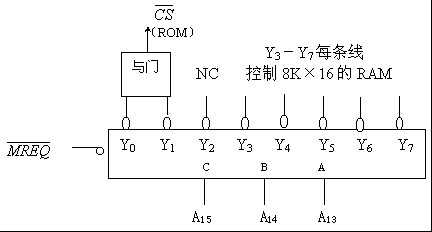

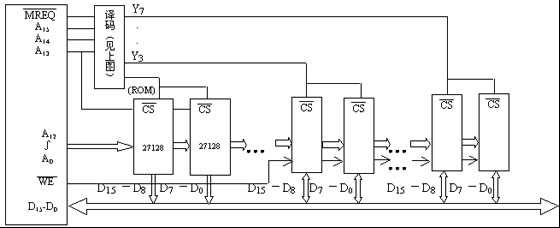

7.某机器中,已知配有一个地址空间为0000H-3FFFH的ROM区域。现在再用一个RAM芯片(8K×8)形成40K×16位的RAM区域,起始地址为6000H,假定RAM芯片有![]() 和

和![]() 信号控制端。CPU的地址总线为A15-A0,数据总线为D15-D0,控制信号为R/

信号控制端。CPU的地址总线为A15-A0,数据总线为D15-D0,控制信号为R/![]() (读/写),?

(读/写),?![]() (访存),要求:

(访存),要求:

(1)?画出地址译码方案。

(2)?将ROM与RAM同CPU连接。

解:(1)依题意,主存地址空间分布如右图所示,可选用2片27128(16K×8位)的EPROM作为

ROM区;10片的8K×8位RAM片组成40K×16位的RAM区。27128需14位片内地址,而RAM需13位

片内地址,故可用A15-A13三位高地址经译码产生片选信号,方案如下:

?

(2)

8.?存储器容量为64M,字长64位,模块数m?=?8,分别用顺序方式和交叉方式进行组织。存储周期T?=?100ns,数据总线宽度为64位,总线周期τ?=?10ns?.问顺序存储器和交叉存储器的带宽各是多少?

解:信息总量:?q?=?64位?×8?=512位

顺序存储器和交叉存储器读出8个字的时间分别是:

t2?=?m?T?=?8×100ns?=8×10![]() ?(s)

?(s)

t1?=?T?+?(m?-?1)![]() ?=?100?+?7×10?=?1.7?×10?

?=?100?+?7×10?=?1.7?×10?![]() (s)

(s)

顺序存储器带宽是:

W2?=?q?/?t2?=?512÷(8×10?![]() )=?64?×10

)=?64?×10![]() (位/?S)

(位/?S)

交叉存储器带宽是:

W1?=?q?/?t1?=?512÷(1.7?×10![]() )=?301?×10

)=?301?×10![]() ?(位/?S)

?(位/?S)

9.?CPU执行一段程序时,?cache完成存取的次数为2420次,主存完成存取的次数为80

次,已知cache存储周期为40ns,主存存储周期为240ns,求cache/主存系统的效率和平均访问时间。

解:先求命中率h

h=nc/(nc?+nm?)=2420÷(2420+80)=0.968

则平均访问时间为ta

ta=0.968×40+(1-0.968)?×240=46.4(ns)

r?=240÷40=6

cache/主存系统的效率为e

e=1/[r+(1-r)×0.968]=86.2%

10.已知Cache存储周期40ns,主存存储周期200ns,Cache/主存系统平均访问时间为50ns,求Cache的命中率是多少?

解:?∵?ta?=?tc×?h?+tr×(1-h)

?∴?h?=(ta-tr)/(tc-tr)=(50-200)/(40-200)=15/16=0.94

11.主存容量为4MB,虚存容量为1GB,则虚存地址和物理地址各为多少位?如页面大小为4KB,则页表长度是多少?

解:已知主存容量为4MB,虚存容量为1GB

?∵?![]() =4M?∴物理地址为22位

=4M?∴物理地址为22位

又?∵?![]() =1G?∴虚拟地址为30位

=1G?∴虚拟地址为30位

页表长度为?1GB÷4KB=230÷212=218=256K

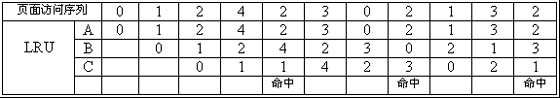

14.假设主存只有a,b,c三个页框,组成a进c出的FIFO队列,进程访问页面的序列是0,1,2.4,2,3,0,2,1.3,2号。用列表法求采用LRU替换策略时的命中率。

解:

∴命中率为

![]()

15.从下列有关存储器的描述中,选择出正确的答案:

A.?多体交叉存储主要解决扩充容量问题;

B.?访问存储器的请求是由CPU发出的;

C.?Cache与主存统一编址,即主存空间的某一部分属于Cache;

D.?Cache的功能全由硬件实现。

解:?D

16.从下列有关存储器的描述中,选择出正确的答案:

A.在虚拟存储器中,外存和主存一相同的方式工作,因此允许程序员用比主存空间大得

?多的外存空间编程;

B.在虚拟存储器中,逻辑地址转换成物理地址是由硬件实现的,仅在页面失效时才由操

?作系统将被访问页面从外存调到内存,必要时还要先把被淘汰的页面内容写入外存;

C.存储保护的目的是:在多用户环境中,既要防止一个用户程序出错而破坏系统软件或

?其他用户程序,又要防止一个用户访问不是分配给他的主存区,以达到数据安全和保

?密的要求。

解:C

第四章

1.ASCll码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理?为什

么?

解:指令字长设计为12位不是很合理。主存单元字长为32位,一个存储单元可存放4个ASCII码,

余下4位可作为ASCII码的校验位(每个ASCII码带一位校验位),这样设计还是合理的。

但是,设计指令字长为12?位就不合理了,12位的指令码存放在字长32位的主存单元中,

造成19位不能用而浪费了存储空间。

2.假设某计算机指令长度为20位,具有双操作数、单操作数、无操作数三类指令形式,每个操作数地址规定用6位表示。问:

若操作码字段固定为8位,现已设计出m条双操作数指令,n条无操作数指令,在此情况下,这台计算机最多可以设计出多少条单操作数指令?

解:这台计算机最多可以设计出256-m-n条单操作数指令

3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

![]()

解:指令格式及寻址方式特点如下:

①?单字长二地址指令;

②?操作码OP可指定![]() =64条指令;

=64条指令;

③?RR型指令,两个操作数均在寄存器中,源和目标都是通用寄存器(可分别指定16个寄存器

? 之一);

④?这种指令格式常用于算术逻辑类指令。

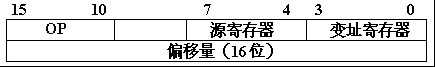

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:指令格式及寻址方式特点如下:

①?双字长二地址指令;

②?操作码OP可指定![]() =64条指令;

=64条指令;

③?RS型指令,两个操作数一个在寄存器中(16个寄存器之一),另一个在存储器中;

④?有效地址通过变址求得:E=(变址寄存器)±?D,变址寄存器可有16个。

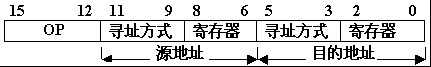

5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:指令格式及寻址方式特点如下:

①?单字长二地址指令;

②?操作码OP可指定![]() =16条指令;

=16条指令;

③?有8个通用寄存器,支持8种寻址方式;

④?可以是RR型指令、SS型指令、RS型指令、

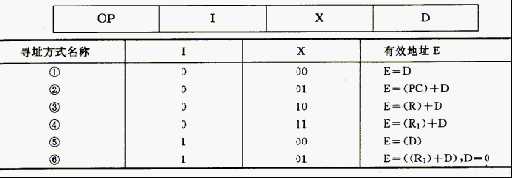

6.一种单地址指令格式如下所示,其中I为间接特征,X为寻址模式,D为形式地址。I,X,D组成该指令的操作数有效地址E。设R为变址寄存器,R1?为基值寄存器,PC为程序计数器,请在下表中第一列位置填入适当的寻址方式名称。

解:?①?直接寻址

?②?相对寻址

?③?变址寻址

?④?基址寻址

?⑤?间接寻址

?⑥?基址间址寻址

7.某计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有40条指令,试采用直接、立即、变址、相对四种寻址方式设计指令格式。

解:40条指令需占用操作码字段(OP)6位,这样指令余下长度为10位。为了覆盖主存640K字的地

址空间,设寻址模式(X)2位,形式地址(D)8位,其指令格式如下:

![]() ?

?

寻址模式定义如下:

X=?0?0?直接寻址?有效地址?E=D(直接寻址为256个存储单元)

X=?0?1?立即寻址?D字段为操作数

X=?1?0?变址寻址?有效地址?E=?(RX)+D?(可寻址64K个存储单元)

X=?1?1?相对寻址?有效地址?E=(PC)+D?(可寻址64K个存储单元)

其中RX为变址寄存器(16位),PC为程序计数器(16位),在变址和相对寻址时,位移量D可 正可负。

8.某机字长为32位,主存容量为1M,单字长指令,有50种操作码,采用页面寻址、立即、直接等寻址方式。CPU中有PC,IR,AR,?DR和16个通用寄存器,页面寻址可用PC高位部分与形式地址部分拼接成有效地址。问:

(1)指令格式如何安排?

(2)主存能划分成多少页面?每页多少单元?

(3)能否增加其他寻址方式?

解:?(1)依题意,指令字长32位,主存1M字,需20位地址A19-A0。50种操作码,需6位OP,指令

?寻址方式Mode为2位,指定寄存器Rn需4位。设有单地址指令、双地址指令和零地址指

?令,现只讨论前二种指令。

单地址指令的格式为:

![]()

Mode=00时为立即寻址方式,指令的23-0位为立即数;

Mode=01时为直接寻址方式,指令的19-0位为有效地址。

双地址指令的格式为:

![]()

Mode1=01时为寄存器直接寻址方式,操作数S=(Rn);

Mode1=11时为寄存器间址寻址方式,?有效地址E=(Rn)。

Mode2=00时为立即寻址方式,指令的13-0位为立即数;

Mode2=01时为页面寻址方式;

Mode2=10时为变址寻址方式,E=(Rn)+D;

Mode2=11时为变址间址寻址方式,?E=((Rn)+D)。

(2)由于页面寻址方式时,D为14位,所以页面大小应为![]() =16K字,则1M字可分为

=16K字,则1M字可分为

?![]() =64个页面。可由PC的高6位指出页面号。

=64个页面。可由PC的高6位指出页面号。

(3)能增加其它寻址方式,例上述间址方式、变址间址寻址方式。

14.?从以下有关RISC的描述中,选择正确答案。

A.采用RISC技术后,计算机的体系结构又恢复到早期的比较简单的情况。

B.为了实现兼容,新设计的RISC,是从原来CISC系统的指令系统中挑选一部分实现的。

C.RISC的主要目标是减少指令数,提高指令执行效率。

D.RISC设有乘、除法指令和浮点运算指令。?

解:?C

15.?根据操作数所在位置,指出其寻址方式(填空):

(1)操作数在寄存器中,为(A)寻址方式。

(2)操作数地址在寄存器,为(B)寻址方式。

(3)操作数在指令中,为(C)寻址方式。

(4)操作数地址(主存)在指令中,为(D)寻址方式

(5)操作数的地址,为某一寄存器内容与位移量之和可以是(E,F,G)寻址方式。

解:A:寄存器直接;?B:?寄存器间接;?C:立即;

D:?直接;? ?E:相对;? ?F:基值;G:变址

第五章

1.请在括号内填入适当答案。在CPU中:

(1)?保存当前正在执行的指令的寄存器是(指令寄存器IR);

(2)?保存当前正要执行的指令地址的寄存器是(程序计数器PC);

(3)?算术逻辑运算结果通常放在(通用寄存器?)和(数据缓冲寄存器DR?)。

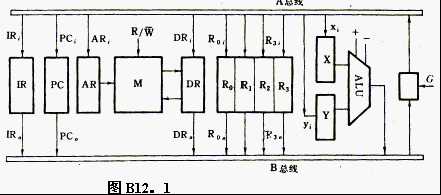

2.参见下图(课本P166图5.15)的数据通路。画出存数指令"STA?R1?,(R2)"的指令周期

?流程图,其含义是将寄存器R1的内容传送至(R2)为地址的主存单元中。标出各微操作信

?号序列。

解:"STA?R1?,(R2)"指令是一条存数指令,其指令周期流程图如下图所示:

3.参见课本P166图5.15的数据通路,画出取数指令"LDA(R3),RO"的指令周期流程图,

?其含义是将(R3)为地址的主存单元的内容取至寄存器R0中,标出各微操作控制信号序列。

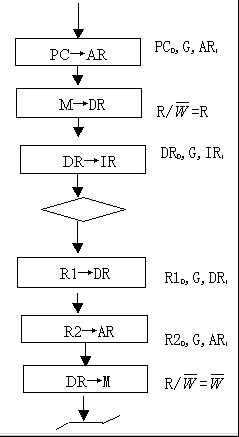

5.如果在一个CPU周期中要产生3个脉冲?T1?=?200ns?,T2?=?400ns?,T3?=?200ns,试画出

?时序产生器逻辑图。

解:节拍脉冲T1?,T2?,T3?的宽度实际等于时钟脉冲的周期或是它的倍数,此时T1?=?T3?=200ns?,

?T2?=?400?ns?,所以主脉冲源的频率应为?f?=?1?/?T1?=5MHZ?。为了消除节拍脉冲上的毛刺,环

?型脉冲发生器可采用移位寄存器形式。下图画出了题目要求的逻辑电路图和时序信号关系。根据关

?系,节拍脉冲T1?,T2?,T3?的逻辑表达式如下:

T1?=?C1·![]() ?,?T2?=?

?,?T2?=?![]() ,?T3?=?

,?T3?=?![]()

6.假设某机器有80条指令,平均每条指令由4条微指令组成,其中有一条取指微指令是所有指

?令公用的。已知微指令长度为32位,请估算控制存储器容量。

解:微指令条数为:(4-1)×80+1=241条

?取控存容量为:256×32位=1KB

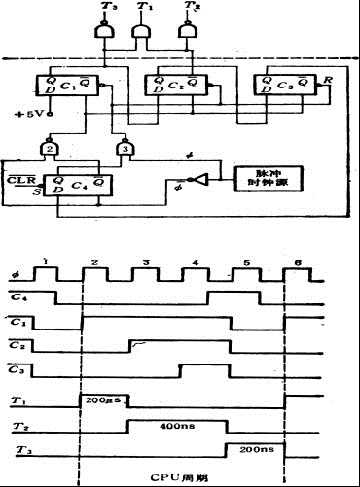

7.?某ALU器件使用模式控制码M,S3,S2,S1,C来控制执行不同的算术运算和逻辑操作。

?下表列出各条指令所要求的模式控制码,其中y为二进制变量,F为0或1任选。

?试以指令码(A,B,H,D,E,F,G)为输入变量,写出控制参数M,S3,S2,S1,C的逻

?辑表达式。

解:?M=G

?S3=H+D+F

?S2=1

?![]()

?C=H+D+(E+F)y

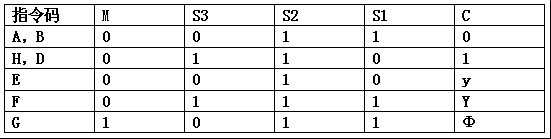

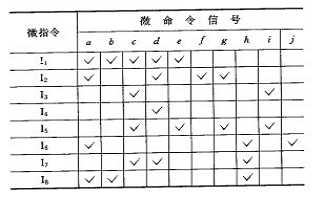

8.某机有8条微指令I1-I8,每条微指令所包含的微命令控制信号如下表所示。

?

?

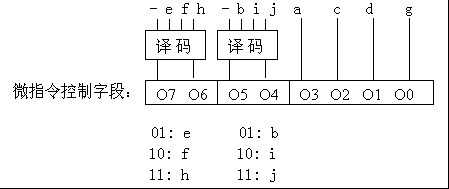

?a-j分别对应10种不同性质的微命令信号。假设一条微指令的控制字段为8位,请安排微指 ?令的控制字段格式。

解:经分析,(e?,f?,h)和(b,?i,?j)可分别组成两个小组或两个字段,然后进行译码,可得六个

?微命令信号,剩下的a,?c,?d,?g?四个微命令信号可进行直接控制,其整个控制字段组成如

?下:

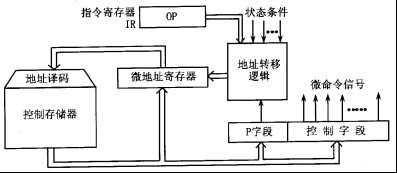

11.已知某机采用微程序控制方式,其控制存储器容量为?512×48(位)。微程序可在整个控

?制存储器中实现转移,可控制微程序转移的条件共4个,微指令采用水平型格式,后继微

?指令地址采用断定方式。请问:

?(1)微指令中的三个字段分别应为多少位?

?(2)画出围绕这种微指令格式的微程序控制器逻辑框图。

解:

(l)假设判别测试字段中每一位作为一个判别标志,那么由于有4个转移条件,故该字段为4位;

?又因为控存容量为512单元,所以下地址字段为9位,。微命令字段则是:

(48-4-9)=?35位。

(2)对应上述微指令格式的微程序控制器逻辑框图如下图所示。其中微地址寄存器对应下地址

?字,P字段即为判别测试字段,控制字段即为微命令字段,后两部分组成微指令寄存器。地? ? ? 址转移逻辑的输入是指令寄存器的OP码、各种状态条件以及判别测试字段所给的判别标志

(某一位为1),其输出用于控制修改微地址寄存器的适当位数,从而实现微程序的分支转移 (此例微指令的后继地址采用断定方式)。

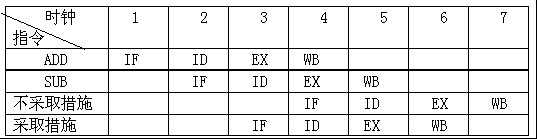

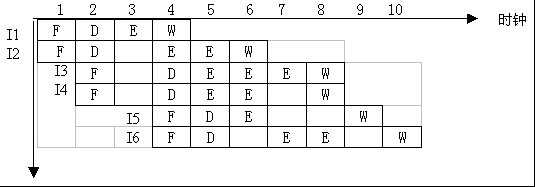

12.今有4级流水线分别完成取值、指令译码并取数、运算、送结果四步操作,

今假设完成各步操作的时间依次为100ns,100ns,80ns,50ns。

请问:(1)流水线的操作周期应设计为多少?

(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么第二条指令要

? 推迟多少时间进行。

(3)如果在硬件设计上加以改进,至少需推迟多少时间?

解:

(1)?流水线的操作时钟周期?t应按四步操作中最长时间来考虑,?所以t=100ns;

(2)?两条指令发生数据相关冲突情况::

ADD?R1,R2,R3?;?R2+R3→R1

SUB?R4,R1,R5?;?R1-R5→R4

两条指令在流水线中执行情况如下表所示:

ADD指令在时钟4时才将结果写入寄存器R1中,?但SUB指令在时钟3时就需读寄存器R1了,显然发生

数据相关,不能读到所需数据,只能等待。如果硬件上不采取措施,第2条指令SUB至少应推迟2个

操作时钟周期,即t=2×100ns=200ns;

(3)如果硬件上加以改进(采取旁路技术),这样只需推迟1个操作时钟周期就能得到所需数据,

?即t=100ns。

15.用定量描述法证明流水计算机比非流水计算机具有更高的吞吐率。

解:衡量并行处理器性能的一个有效参数是数据带宽(最大吞吐量),它定义为单位时间内可以产生

的最大运算结果个数。

设P1是有总延时T1的非流水处理器,故其带宽为1/T1。又设Pm是相当于P1?m?段流水处理器延迟时 间Tr,故Pm的带宽为1/(Tc+Tr)。如果Pm是将P1划分成相同延迟的若干段形成的,则T1≈mTc?因

此P1的带宽接近于1/mTc,由此可见,当mTc>Tc+Tr满足时,Pm比P1具有更大的带宽。

16.?流水线中有三类数据相关冲突:写后读(RAW)相关;读后写(WAR)相关;写后写

(WAW)相关。判断以下三组指令各存在哪种类型的数据相关。?

(1)?I1?LAD?R1,A?;?M(A)→R1,M(A)是存储器单元

?I2?ADD?R2,R1?;(R2)+(R1)→R2

(2)?I3?ADD?R3,R4?;(R3)+(R4)→R3

?I4?MUL?R4,R5?;(R4)×(R5)→?R4

(3)?I5?LAD?R6,B?;?M(B)→R6,M(B)是存储器单元

?I6?MUL?R6,R7?;(R6)×(R7)→?R6

解:(1)写后读(RAW)相关;

(2)读后写(WAR)相关,但不会引起相关冲突;

(3)写后读(RAW)相关、写后写(WAW)相关

17.参考教科书图5.42所示的超标量流水线结构模型,现有如下6条指令序列:

I1?LAD?R1,?B;?M(B)?→?R1,M(B)是存储器单元

I2?SUB?R2,?R1;?(R2)-(R1)?→?R2

I3?MUL?R3,?R4;?(R3)×(R4)?→?R3

I4?ADD?R4,?R5;?(R4)+(R5)?→?R4

I5?LAD?R6,?A;?M(A)?→?R6,M(A)是存储器单元

I6?ADD?R6,?R7;?(R6)+(R7)?→R6

请画出:(1)?按序发射按序完成各段推进情况图。

(2)?按序发射按序完成的流水线时空图。

解:(1)

(2)

第六章

1.比较单总线、双总线、三总线结构的性能特点。

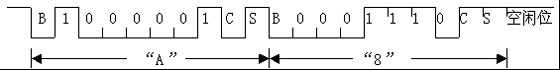

3.?用异步通信方式传送字符"A"和"8",数据有7位,偶校验1?位。起始位1位,

停止位l位,请分别画出波形图。

解:?字符A的ASCII码为?41H=1000001B;?

?字符8的ASCII码为?38H=0111000B;

?串行传送波形图为:

注:?B:起始位

?C:校验位?

?S:停止位?

8.同步通信之所以比异步通信具有较高的传输频率,是因为同步通信____。

A.不需要应答信号;

B.总线长度较短;

C.用一个公共时钟信号进行同步;

D.各部件存取时间比较接近。

解:?C

9.?在集中式总线仲裁中,____方式响应时间最快,____方式对____最敏感。

A.菊花链方式?B.独立请求方式?C.电路故障?D.计数器定时查询方式

解:?B?A?C

10.?采月串行接口进行7位ASCII码传送,带有1位奇校验位,l位起始位和1位停止位,当传输率为9600波特时,字符传送速率为____。

A.960?B.873.?C.1372?D.480

解:?A

11.系统总线中地址线的功能是______。

A.?选择主存单元地址?

B.?选择进行信息传输的设备

C.?选择外存地址

D.?指定主存和I/O设备接口电路的地址

解:?D

12.系统总线中控制器的功能是______。

A.?提供主存、I/O接口设备的控制信号和响应信号

B.?提供数据信息

C.?提供时序信号

D.?提供主存、I/O接口设备的响应信号

解:?D

14.?PCI是一个与处理器无关的_____,它采用____时序协议和____式仲裁策略,并具有____能力。

A.集中?B.自动配置?C.同步?D.高速外围总线

解:D?C?A?B

15.?PCI总线的基本传输机制是____传送。利用____可以实现总线间的____传送,使所有的存取都按CPU的需要出现在总线上。PCI允许____总线____工作。

A.桥?B.猝发式?C.并行?D.多条?E.?猝发式?

解:?B?A?C?D?E

17.PCI总线中三种桥的名称是什么?桥的功能是什么?

解:PCI总线有三种桥,即HOST?/?PCI桥(简称HOST桥),PCI?/?PCI桥和PCI?/?LAGACY桥。

在PCI总线体系结构中,桥起着重要作用:

(1)?接两条总线,使总线间相互通信;

(2)?是一个总线转换部件,可以把一条总线的地址空间映射到另一条总线的地址空间上,

从而使系统中任意一个总线主设备都能看到同样的一份地址表。?

(3)?利用桥可以实现总线间的卒发式传送。

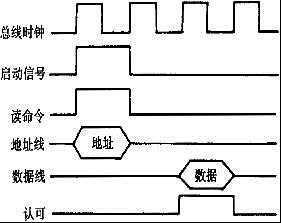

19.总线的一次信息传送过程大致分哪几个阶段?若采用同步定时协议,请画出

读数据的同步时序图。

解:分五个阶段:请求总线、总线仲裁、寻址(目的地址)、信息传送、状

态返回(错误报告)。读数据的同步时序图为:

20.某总线在一个总线周期中并行传送8个字节的数据,假设一个总线周期等于一个总线时钟周期,总线时钟频率为70MHZ?,求总线带宽是多少?

解:设总线带宽用Dr表示,总线时钟周期用T?=?1/f表示,一个总线周期传送的数据量用D表示,

根据定义可得:

Dr?=?T?/?D?=?D?×1/f=8B×70×106/s?=?560MB/

第七章

1.?计算机的外围设备是指(?)

A.输入/输出设备? B.?外存储器

C.?输入/输出设备及外存储器? D.?除了CPU和内存以外的其他设备

解:?D

2.打印机根据印字方式可以分为(?)和(?)两大类,在(?)类打印机中,只有(?)型打印机能打印汉字,请从下面答案中选择填空。

A.?针型打印机?B.?活字型打印机

C.?击打式? ?D.?非击打式

解:C?D?C?A

5.试推导磁盘存贮器读写一块信息所需总时间的公式。

解:设读写一块信息所需总时间为Tb,平均找道时间为Ts,平均等待时间为TL,读写一块信息的

传输时间为Tm,则:Tb=Ts+TL+Tm。假设磁盘以每秒r转速率旋转,每条磁道容量为N个字,

则数据传输率=rN个字/秒。又假设每块的字数为n,因而一旦读写头定位在该块始端,就能在

Tm≈(n?/?rN)秒的时间中传输完毕。TL是磁盘旋转半周的时间,TL=(1/2r)秒,

由此可得:?

Tb=Ts+1/2r+n/rN?秒

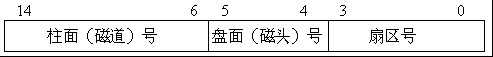

7.某磁盘存贮器转速为3000转?/?分,共有4个记录面,每毫米5道,每道记录信息为12288字节,最小磁道直径为230mm,共有275道。问:

(1)?磁盘存贮器的容量是多少?

(2)?最高位密度与最低位密度是多少?

(3)?磁盘数据传输率是多少?

(4)?平均等待时间是多少?

(5)?给出一个磁盘地址格式方案。

解:

(1)?每道记录信息容量?=?12288字节

每个记录面信息容量?=?275×12288字节

共有4个记录面,所以磁盘存储器总容量为?:

4?×275×12288字节?=?13516800字节

(2)?最高位密度D1按最小磁道半径R1计算(R1?=?115mm):

D1?=?12288字节?/?2πR1?=?17字节?/?mm

最低位密度D2按最大磁道半径R2计算:

R2?=?R1?+?(275?÷?5)?=?115?+?55?=?170mm

D2?=?12288字节?/?2πR2?=?11.5?字节?/?mm

(3)?磁盘传输率?C?=?r?·?N?

r?=?3000?/?60?=?50?周?/?秒

N?=?12288字节(信道信息容量)

C?=?r?·?N?=?50?×?12288?=?614400字节?/?秒

(4)平均等待时间?=?1/2r?=?1?/?(2×50)?=?10毫秒?

(5)磁盘存贮器假定只有一台,所以可不考虑台号地址。有4个记录面,每个记录面有275个磁

?道。假定每个扇区记录1024个字节,则需要12288?÷1024字节?=?12个扇区。由此可得如

?下地址格式:

14.有一台磁盘机,其平均寻道时间为了30ms,平均旋转等待时间为120ms,数据传输速率为500B/ms,磁盘机上存放着1000件每件3000B?的数据。现欲把一件数据取走,更新后在放回原地,假设一次取出或写入所需时间为:

平均寻道时间+平均等待时间+数据传送时间

?另外,使用CPU更新信息所需时间为4ms,?并且更新时间同输入输出操作不相重叠。

?试问:

(1)?盘上全部数据需要多少时间?

(2)?若磁盘及旋转速度和数据传输率都提高一倍,更新全部数据需要多少间?

解:(1)磁盘上总数据量?=?1000×3000B?=?3000000B

?读出全部数据所需时间为?3000000B?÷?500B?/?ms?=?6000ms

?重新写入全部数据所需时间?=?6000ms

?所以,更新磁盘上全部数据所需的时间为?:

2×(平均找道时间?+?平均等待时间?+?数据传送时间?)+?CPU更新时间?

=?2(30?+?120?+?6000)ms?+?4ms?=?12304ms

(2)?磁盘机旋转速度提高一倍后,平均等待时间为60ms;

数据传输率提高一倍后,数据传送时间变为:

3000000B?÷?1000B?/?ms?=?3000ms

更新全部数据所需时间为:

2?×(30?+?60?+?3000)ms?+?4ms?=?6184ms

17.?刷新存储器的重要性能指标是它的带宽。若显示工作方式采用分辨率为1024×768,颜色深度为24位,帧频(刷新速率)为72HZ,求:

(1)刷新存储器的存储容量是多少?

(2)刷新存储器的贷款是多少?

解:(1)因为刷新存储器所需存储容量?=?分辨率?×?每个像素点颜色深度

∴?1024?×?768?×?3B?≈?4MB

(2)因为刷新所需带宽?=?分辨率?×?每个像素点颜色深度?×?刷新速度

∴?1024?×?768?×?3B?×?72?/?S?=?165888KB?/?S?≈?162MB?/?S

第八章

1.如果认为CPU等待设备的状态信号是处于非工作状态(即踏步等待),那么在下面几种主机与设备之间的数据传送中:(?)主机与设备是串行工作的;(?)主机与设备是并行工作的;(?)主程序与设备是并行运行的。

A.程序查询方式?B.?程序中断方式?C.?DMA方式

解:?A?C?B

2.中断向量地址是_____。

A.子程序入口地址?B.?中断服务程序入口地址

C.中断服务程序入口地址指示器?C.?例行程序入口地址

解:?C

3.利用微型机制作了对输入数据进行采样处理的系统。在该系统中,每抽取一个输入数据就要中断CPU一次,中断处理程序接受采样的数据,将其放到主存的缓冲区内。该中断处理需时x秒,另一方面缓冲区内每存储n个数据,主程序就将其取出进行处理,这种处理需时y秒。因此该系统可以跟踪到每秒_____次的中断请求。

A.N/(n×x+y)?B.?N/(x+y)×n?C.?Min(1/x,?n/y)

解:?A

4.采用DMA方式传送数据时,每传送一个数据就要占用一个____的时间。

A.?指令周期?B.?机器周期?

C.?存储周期?D.?总线周期

解:?C

5.通道的功能是:(1)________,(2)______。按通道的工作方式分,通道有______通道、_______通道和______通道三种类型。

解:(1)执行通道指令,组织外围设备和内存进行数据传输;

(2)执行CPU的I/O指令,以及向CPU报告中断。

?选择通道、字节多路通道、数组多路通道

6.在教科书图8.7中,当CPU对设备B的中断请求进行服务时,如设备A提出请求,CPU能够响应中断吗?为什么?如果设备B一提出请求总能立即得到服务,问怎样调整才能满足此要求?

解:(1)CPU不能响应中断

(2)因为同级中断不能嵌套,而A、B设备属于同级中断

(3)如果想要设备B一提出请求即能得到服务,则应该使设备B为最高优先级,这里可将设备 ?B单独接至3级IR,处于最高优先级。

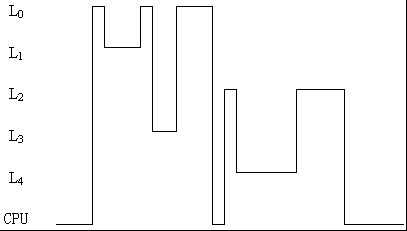

8.设某机有5级中断:L0,L1,L2,L3,L4,?其中断响应优先次序为:L0最高,L1次

之,L4最低。现在要求将中断处理次序改为L1→L3→L0→L4→L2,试问:

(1)?下表中各级中断处理程序的各中断级屏蔽值如何设置(每级对应一位,该位

为"0"表示允许中断,该位为"1"表示中断屏蔽)?

(2)?若这5级中断同时都发出中断请求,按更改后的次序画出进入各级中断处理程

序的过程示意图。

解:(1)

?

?

(2)?

?

?

9.某机器CPU中有16个通用寄存器,运行某中断处理程序时仅用到其中2个寄存器,请问响应中断而进入该中断处理程序时,是否要将通用寄存器内容保存到主存中去?需保存几个寄存器?

解:响应中断而进入该中断处理程序时,需将通用寄存器内容保存到主存中去,但为减少中断处

理时间,不必保存所有通用寄存器内容,这里只需将2个中断处理程序中用到的寄存器内容

保存起来。

12.下列陈述中正确的是_____。

A.?在DMA周期内,CPU不能执行程序

B.?中断发生时,CPU首先执行入栈指令将程序计数器内容保护起来

C.?DMA传送方式中,DMA控制器每传送一个数据就窃取一个指令周期

D.?输入输出操作的最终目的是要实现CPU与外设之间的数据传输

解:?D

13.Pentium系统有两类中断源:①由CPU外部的硬件信号引发的称为_____,它分为可屏蔽______和非屏蔽_____;②由指令引发的称为_______,其中一种是执行______,另一种是_______。

解:①?外部中断?INTR?NMI?

②?异常中断?执行软件中断指令引发的?出错或故障引发的

14.IEEE1394是______I/O标准接口,与SCSI_____I/O标准接口相比,它具有更高的______,更强的_______,提及_____,连接方便。

解:B?A?C?D?E

15.SCSI是系统级_____,是处于主适配器和智能设备控制器之间的_____I/O接口。SCSI-3标准允许SCSI总线上连接的设备由______个提高到_____个,可支持_____位数据传输。

A.?并行?B.?接口?C.?16?D.?8?E.?32

解:?B?A?D?C?D

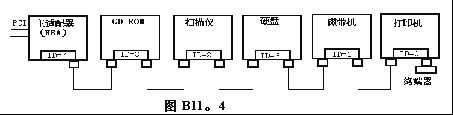

18.若设备的优先级依次为CD-ROM、扫描仪、硬盘、磁带机、打印机,请用标准接口SCSI进行配置,画出配置图。

解:PCI?HBA?→?CD-ROM?→?扫描仪?→?硬盘?→?磁带机?→?打印机?→?终端器

?

?

标签:

原文地址:http://www.cnblogs.com/wlzcool/p/4687754.html